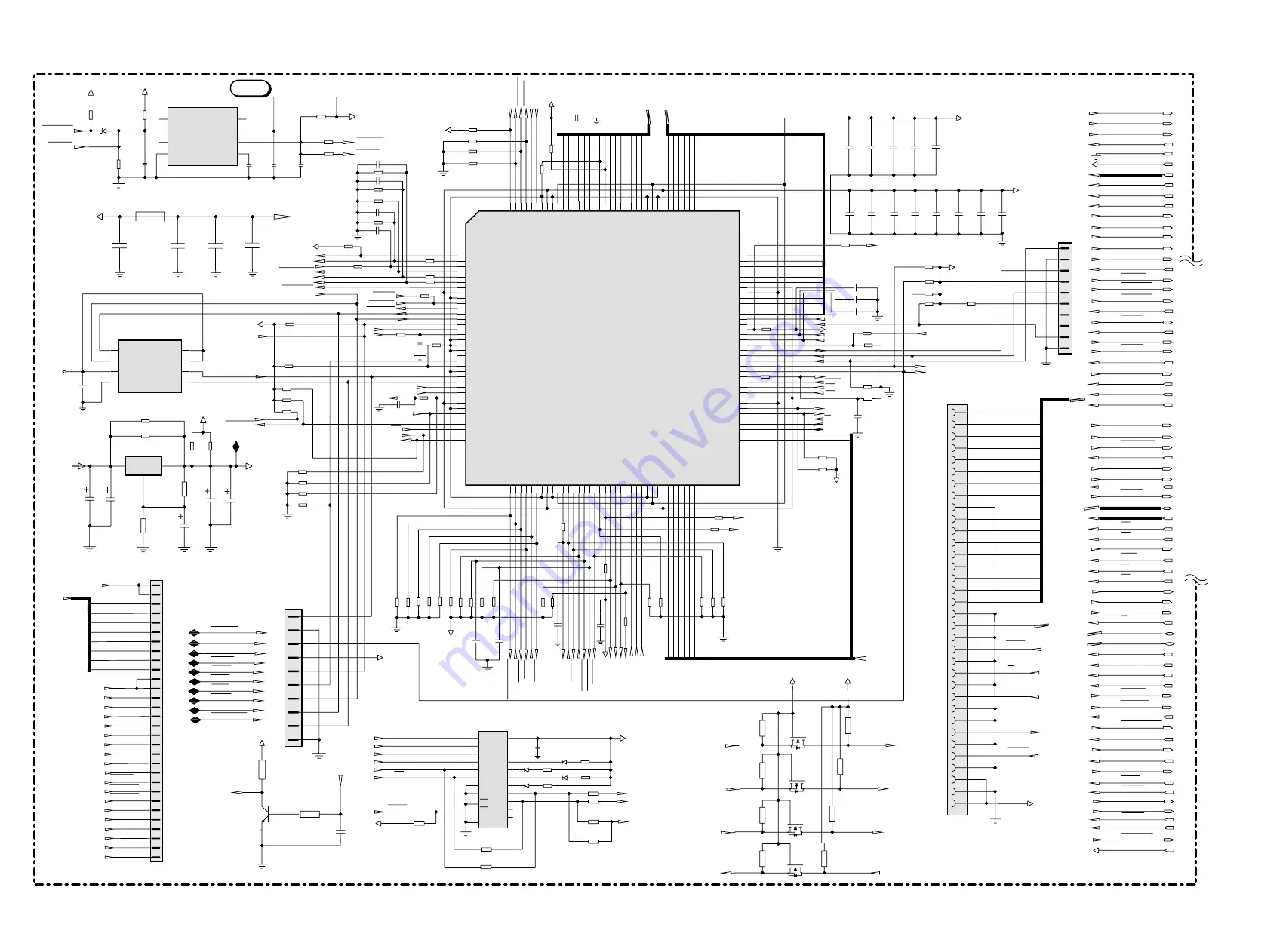

DTH8005

First issue 12 / 04

DGND

RNOTW

V_1H

DGND

DATA0

DCLK

+3V3SD

DGND

+5VED

ATAPI_DIOW

ATAPI_DIOR

VDEC_HS

IDE_RST

ODD_RST

VDEC_RST

VDEC_FLD

SYS_RST

FPGA_RST

ODD_ATAPI_IRQ

ODD_ATAPI_RST

DGND

+3V3SD

EMI_D13

EMI_D6

EMI_D0

EMI_D1

EMI_D2

EMI_D3

EMI_D4

EMI_D5

EMI_D7

EMI_D[0:15]

EMI_D8

EMI_D9

EMI_D10

EMI_D11

EMI_D12

EMI_D14

EMI_D15

EMI_AD1

USB_RST

USB_CS

OE

RNOTW

USB_IRQ

FM_S_CLK_3_3

FM_S_OUT_3_3

FM_CE

FM_S_CLK1

DGND

DGND

DGND

DGND

+1V5

DGND

DGND

DGND

FPGA_RST

BOARD_RST

SV_F/SAPR_HS

SV_R/SAPR_VS

ODD_ATAPI_IRQ

LOGGER_IRQ

LOGGER_CS

CE2

CLAHI_INT

CLAHI_CWE

OSCLK/OSSTB

OSSYNC

PSTOP

CLAU_RST

ATAPI_IORDY

IDE_RST

IDE_IRQ

ODD_RST

ODD_IRQ

USB_CS

USB_RST

USB_IRQ

ODD_ATAPI_RST

DXX_FLD

DXXHSYNC

OE

GS_IRQ2

CE1

EMI_D9

EMI_D8

EMI_D7

EMI_D11

EMI_D13

EMI_D15

EMI_D4

EMI_D6

EMI_D10

EMI_D14

EMI_D12

EMI_D5

EMI_D3

EMI_D2

EMI_D1

EMI_D0

EMI_D[0:15]

FPA_IRQ

KDB_RST

VDEC_RST VDEC_FLD

VDEC_HS

EMI_AD5

EMI_AD3

EMI_AD2 EMI_AD1

EMI_AD[1:21]

EMI_AD4

EMI_AD6

EMI_AD7

EMI_AD9

EMI_AD10

EMI_AD18

EMI_AD19

EMI_AD20

EMI_AD21

EMI_AD17

EMI_AD11

EMI_AD8

OS0

OS1

OS6

OS[0:7]

OS3

OS5

OS7

OS2

OS4

+1V5

DGND

+1V5

DGND

GS_IRQ0

PWR_FAIL

+3V3SD

BC847B

TG101

KDB_RST

GOB_RST

DGND

DGND

100N0

CG125

DGND

GOB_RST

RG174

180R

180R

RG171

180R

RG172

+3V3SD

NCONFIG

CONF_DONE

INIT_DONE

EMI_D0

CE2

DGND

BUF_OE

DGND

INIT_DONE

BUF_OE

NCONFIG

ODD_ATAPI_IRQ

ODD_ATAPI_RST

DGND

4K7

RG163

+3V3SD

SYS_RST

USB_IRQ

ATAPI_DIOR

ATAPI_DIOW

ODD_IRQ

CLAU_RST

CLAHI_INT

CLAHI_CWE

CLAHI_CCS

CLAHI_CRE

PSTOP

OSREQ

OSVLD

OSSYNC

OSCLK/OSSTB

DGND

DGND

VDEC_HS

DXX_FLD

DXX_RST

PPC_CLK

H_1H

FS_BK

LOGGER_IRQ

ODD_RST

CLA_ACLK

ATAPI_DIOR

CLAU_RST

CLAHI_CCS

OSREQ

OSVLD

OSCLK/OSSTB

DGND

OSSYNC

PSTOP

CLAHI_CRE

CLAHI_CWE

CLAHI_INT

ATAPI_DIOW

LOGGER_CS

V_1H

CE1

CE2

MEMWAIT

GS_IRQ1

ADMCLK

VDEC_FLD

VDEC_RST

FPA_IRQ

+3V3SD

100NO

CG107

CG108

100NO

100NO

CG110

CG111

100NO

100NO

CG112

DGND

RG138

4K7

4K7

RG137

4K7

RG139

RG129

4K7

24K3

RG149

RG124

4K7

4K7

RG128

RG132

4K7

RG127

4K7

4K7

RG125

RG126

4K7

100NO

CG105

CG104

100NO

100NO

CG103

CG102

100NO

1SS394

DG101

RG151

20K0

100NO

CG101

CG114

100NO

DGND

OS7

OS5

OS4

OS3

OS2

OS1

OS0

OS6

OS[0:7 ]

RG150

2K2

+3V3SD

RG122

4K7

RG121

10K

BG101

10

9

8

7

6

5

4

3

2

1

+3V3SD

BG102

1

2

3

4

5

6

7

8

9

10

ODD_IRQ

+3V3SD

NSTATUS

+3V3SD

PREP

RG165

RG166

PREP

10K

RG164

RG167

10K

10K

RG168

RG173

180R

100N0

CG164

DCLK

DATA0

+3V3SD

RG157

0R0

DXX_RST

FPGA_RST

RG142

10K

10K

RG146

RG147

10K

EMI_D[0:15]

OS[0:7]

VBI_VC/PIP_BL

IDE_IRQ

IDE_RST

IDE_IRQ

USB_CS

USB_RST

10UF

CG120

10UF

CG119

CG124

100N0

GEM_FS/VBI_BL

4K7

RG162

DGND

4K7

RG103

RG102

4K7

RG104

4K7

GEM/ST9_RST

DGND

M51957B

IG103

5

6

7

8

4

3

2

1

RG161

4K7

4K7

RG117

RG115

4K7

4K7

RG114

+3V3SD

RG116

4K7

+3V3SD

RG131

4K7

4K7

RG140

RG141

4K7

+3V3SD

0R0

RG119

GS_IRQ0

RG177

47K

10K

RG176

10N0

CG129

100NO

CG109

RG120

0R0

DGND

ATAPI_IORDY

ATAPI_IORDY

SYS_RST

DGND

CLA_ACLK

EMI_AD[1:21]

DXXHSYNC

GS_IRQ2

OE

WE1

WE0

RNOTW

WE0

GS_IRQ1

PCMCLK

CG106

100NO

BOARD_RST

+3V3SD

RG160

10K0

74LVTH244A

1A1

1A2

1A3

1A4

2A1

2A2

2A3

2A4

1OE

2OE

GND

VCC

1Y1

1Y2

1Y3

1Y4

2Y1

2Y2

2Y3

2Y4

IG105

3

5

7

9

12

14

16

18

20

10

19

1

17

15

13

11

8

6

4

2

-

DG173

-

DG171

-

DG172

CG121

10UF

TPG16

TPG17

TPG18

TPG21

TPG22

TPG23

TPG24

TPG25

TPG26

-

DG174

+1V5

PPC_CLK

100N0

CG115

22P0

CG169

DGND

FG001

310R

1U0

CG165

CG166

1U0

100N

CG167

10N

CG168

VCCA_PLL1

NCONFIG

100NO

CG117

100NO

CG116

OSVLD

RG134

33R0

CG118

100P0

PREP

RG156

PREP

RG112

RG111

3K3

RG144

3K3

3K3

RG145

RG153

30R1

0R

RG148

RG170

0R0

0R0

RG169

RG113

0R0

DGND

NICAM_RST

SV_R/SAPR_VS

SV_F/SAPR_HS

+3V3SD

FM_S_OUT1

FM_S_IN1

WE1

NSTATUS

RG154

PREP

FM_S_IN_3_3

FM_CE_3_3

RG136

PREP

PREP

RG130

CLAHI_CRE

RG182

0R0

RG183

0R0

RG184

0R0

NICAM_RST

+3V3SD

+3V3SD

FM_CE_3_3

FM_S_CLK_3_3

FM_S_IN_3_3

FM_S_OUT_3_3

FM_S_OUT1

FM_S_IN1

FM_S_CLK1

G

D

S

TG001

PMBF170N

G

D

S

PMBF170N

TG002

G

D

S

PMBF170N

TG003

G

D

S

PMBF170N

TG004

0R0

RG185

2K2

RG186

2K2

RG187

2K2

RG188

2K2

RG189

2K2

RG190

2K2

RG191

2K2

RG192

2K2

RG193

+5VED

PWR_FAIL

CG113

100NO

DGND

PREP

RG155

FM_CE

BG103

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

PREP

CG128

CG123

18P0

CLAHI_CCS

CG171

100PF

DGND

DGND

CG170

PREP

CG172

100PF

TPG07

LD1117DT

OUT

ADJ

IN

IG104

BB105D

14

34

33

32

31

30

29

28

27

26

25

24

23

22

21

9

8

7

6

5

4

3

20

2

19

18

17

16

15

13

12

11

10

1

PREP

RG101

PREP

RG143

EPCS1

VCC

DATA

GND

ASDI

DCLK

VCC

NCS

VCC

PREP

IG102

1

2

6

3

8

5

7

4

4K7

RG133

EP1C3T144

CLK0

CLK1

CLK2

CLK3

CONF_DONE

DATA0

DCLK

DPCLK4/IO

DPCLK5/IO

GN

GNDA_PLL1

GNDG_PLL1

IO

IO/ASDO

IO/CLKUSR

IO/DPCLK0

IO/DPCLK1

IO/DPCLK2

IO/DPCLK3

IO/DPCLK7

IO/INIT_DONE

IO/NCSO

MSEL0

MSEL1

NCE

NCEO

NCONFIG

NSTATUS

TCK

TDI

TDO

TMS

VCCA_PLL1

VCCIO1

VCCIO3

VCCIO2

VCCINT

VCCIO4

VCCINT

GND

GND

IO

GND

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO IO

IO

IO

IO

IO IO

IO

IO IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

GND

GND

IO

GND

GND

GND

GND

GND

GND

VCCIO1

VCCIO4

VCCINT

VCCINT

VCCI03

VCCI02

IG101

27

36

35

34

33

32

31

30

29

28

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

122

120

121

123

124

125

126

127

128

130

129

131

132

133

134

135

136

137

138

139

140

141

142

143

144

150R

RG152

4K7

RG135

OSREQ

NSTATUS

RG175

0R0

3K3

RG110

RG198

0R0

RG199

0R0

RG106

4K7

4K7

RG107

4K7

RG109

CG126

100NO

CG175

1NO

CG176

1NO

CG173

1NO

CG174

1NO

GEM_FS/VBI_BL

GEM/ST9_RST

FS_BK

H_1H

INIT_DONE

0R0

RG197

0R0

RG200

CG177

1NO

68R0

RG195

DGND

VBI_VC/PIP_BL

RG196

0R0

RG202

PREP

+3V3SD

RG201

PREP

RG204

PREP

RG203

PREP

TPG05

+1V5

+2V5SD

DXX656_BUF

+2V5SD

DXX656_BUF

DXX656_BUF

1K0

RG123

RG108

1K0

VCCA_PLL1

RG180

36R0

(PREP)

P81

P66

P44

P29

P8

P137

P115

P102

P64

P46

P15

P135

GOBSTOPPER

(PREP)

P117

(PREP)

DGND

+3V3SD

0R0

RG194

MEMWAIT

CONF_DONE

CG127

PREP

PREP

CG178

PREP

CG179

PCMCLK

ADMCLK

+1V5

IDR03 2ND GEN DIGITAL

GOBSTOPPER MPEG

(DIGITAL BOARD 4/9)

MAIN SCHEMATIC DIAGRAM - SCHEMA DE LA PLATINE PRINCIPALE - SCHALTBILD HAUPTPLATINE - SCHEMA DELLA PIASTRA PRINCIPALE- ESQUEMA DE LA PLATINA PRINCIPAL