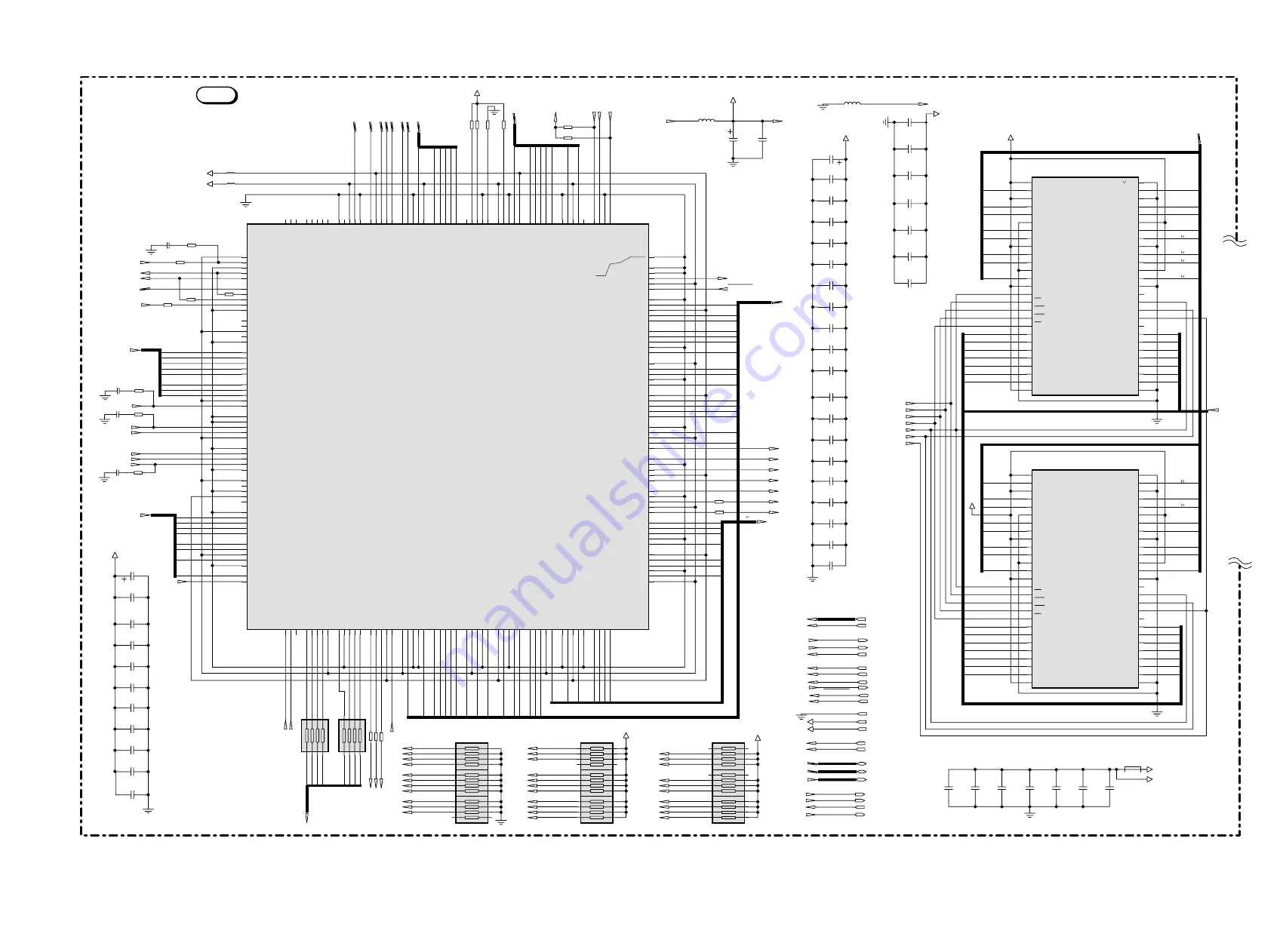

DTH8005

First issue 12 / 04

CLAUDIA_25V

+3V3SDCL

+3V3SD

DGND

CE075

104

104

CE076

CE077

104

104

CE079

CE080

104

104

CE081

80R0

FE075

104

CE078

DGND

+3V3SDCL

104

CE084

CE083

104

CE085

104

104

CE086

104

CE087

CE088

104

104

CE089

CE054

104

CE039

104

CE031

104

CE032

104

CE033

104

CE025

104

104

CE024

CE028

104

104

CE029

CE034

104

104

CE035

CE036

104

104

CE038

CE026

104

CE027

104

104

CE030

104

CE023

104

CE040

104

CE051

CE044

104

CE047

104

104

CE048

CE045

104

CE046

104

104

CE049

104

CE042

104

CE043

CE050

104

MD23

MD17

MD25

MD16

MD15

MD14

MD13

MD12

MD11

MD10

MD9

MD8

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD31

MD30

MD29

MD27

MD28

MD26

MD24

MD18

MD19

MD20

MD21

MD22

MD[0:31]

ADLRCLK

27CK_CLA

OSREQ

ISVLD

PSTOP

RE011

PREP

CE011

PREP

PREP

RE012

PREP

CE012

ADSCLK

CLA_STCLK

PGND

PVDD2

MDQM

MCLK

MCKE

MCS_

MRAS_

MCAS_

MWE_

ADSCLK

RE030

10K0

CLAHI_CRE

ISVLD

ISCLK/ISSTB

DGND

ISSYNC

IS7

IS4

IS6

IS5

IS3

IS0

IS2

IS1

DGND

DGND

CLA_ADAT

CLAHI_INT

CE053

104

CLAUDIA_25V

DGND

PGND

DGND

MCS_

MRAS_

MCAS_

MWE_

MDQM

MCLK

OVHSYNC

CLAHI_CCS

+2V5SD

10K0

NE001

8

7

6

5

1

2

3

4

10K0

NE004

4

3

2

1

5

6

7

8

NE006

10K0

8

7

6

5

1

2

3

4

NE007

10K0

8

7

6

5

1

2

3

4

NE008

10K0

4

3

2

1

5

6

7

8

OVVSYNC

OS[0:7]

CLAHI_CRE

CLAHI_CWE

CLAHI_CCS

CLA_STCLK

DGND

CE052

47U0

NE012

10K0

4

3

2

1

5

6

7

8

NE013

10K0

8

7

6

5

1

2

3

4

EMI_AD[1:21]

EMI_AD1

EMI_AD2

EMI_AD3

EMI_AD4

EMI_AD5

EMI_AD6

EMI_D0

EMI_D1

EMI_D2

EMI_D3

EMI_D4

EMI_D5

EMI_D6

EMI_D7

EMI_D6

EMI_D5

EMI_D4

EMI_D2

EMI_D1

EMI_D0

EMI_D[0:15]

EMI_D7

EMI_D3

EMI_D[0:15]

10K0

NE003

8

7

6

5

1

2

3

4

CLAHI_CCS

CLAUDIA_33V

10K0

RE029

4K7

RE039

RE040

4K7

RE041

4K7

51K0

RE042

DGND

+3V3SD

ADSCLK

ADLRCLK

EMI_AD[1:21]

EMI_AD6

EMI_AD5

EMI_AD4

EMI_AD3

EMI_AD2

EMI_AD1

IS6

IS5

IS4

IS3

IS2

IS1

IS0

IS[0:7]

IS7

SDRAM

VDD1

DQ0

VDDQ1

DQ1

DQ2

VSSQ1

DQ3

DQ4

VDDQ2

DQ5

DQ6

VSSQ2

DQ7

VDD2

DQML

WE

CAS

RAS

CS

BA0

BA1

A10

A0

A1

A2

A3

VDD3

VSS1

A4

A5

A6

A7

A8

A9

A11

NC1

CKE

CLK

DQMH

NC2

VSS2

DQ8

VDDQ3

DQ9

DQ10

VSSQ3

DQ11

DQ12

VDDQ4

DQ13

DQ14

VSSQ4

DQ15

VSS3

MT48LC4M16A2-7E

IE005

54

53

27

3

44

13

14

16

17

18

19

20

21

24

25

10

28

29

30

31

32

23

33

34

35

36

37

38

39

40

41

42

43

45

46

47

48

49

50

51

52

1

2

4

5

6

7

8

9

11

12

15

22

26

CLAHI_INT

+3V3SD

+3V3SDCL

CLAHI_CWE

CLAU_RST

ADLRCLK

0R0

RE026

PREP

RE010

ADSDATA1

CE013

PREP

CLAUDIA_25V

MA[0:13]

MA4

MA5

MA6

MA7

MA8

MA9

MA11

MA2

MA3

MA10

MA12

MA13

MA0

MA1

CLAUDIA_33V

PSTOP

+2V5SD

RE013

PREP

RE033 22R0

0R0

RE034

+3V3SDCL

MD[0:31]

MD8

MD9

MD10

MD11

MD12

MD13

MD21

MD31

MD29

MD16

MD18

MD23

MD17

MD26

MD28

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD15

MD14

MD20

MD22

MD25

MD27

MD19

MD24

MD30

OSREQ

0R0

RE028

CLA_ADAT

P4

27CK_CLA

OSVLD

OSVLD

PVDD2

PVDD2

CLAPO

P1

P2

P3

OVHSYNC

OVVSYNC

SDRAM

VDD1

DQ0

VDDQ1

DQ1

DQ2

VSSQ1

DQ3

DQ4

VDDQ2

DQ5

DQ6

VSSQ2

DQ7

VDD2

DQML

WE

CAS

RAS

CS

BA0

BA1

A10

A0

A1

A2

A3

VDD3

VSS1

A4

A5

A6

A7

A8

A9

A11

NC1

CKE

CLK

DQMH

NC2

VSS2

DQ8

VDDQ3

DQ9

DQ10

VSSQ3

DQ11

DQ12

VDDQ4

DQ13

DQ14

VSSQ4

DQ15

VSS3

MT48LC4M16A2-7E

IE003

26

22

15

12

11

9

8

7

6

5

4

2

1

52

51

50

49

48

47

46

45

43

42

41

40

39

38

37

36

35

34

33

23

32

31

30

29

28

10

25

24

21

20

19

18

17

16

14

13

44

3

27

53

54

CLAPO

MCKE

DGND

PREP

CE010

DGND

DGND

DGND

DMS

DDI

DRSTZ

DCLK

DGND

DGND

DGND

ISSYNC

ISCLK/ISSTB

MA[0:13]

MA12

MA4

MA13

MA0

MA1

MA2

MA3

MA5

MA6

MA7

MA8

MA9

MA11

MA11

MA9

MA8

MA7

MA6

MA5

MA3

MA2

MA1

MA0

MA12

MA10

MA13

MA4

MA10

CE037

104

10U0H

LE003

10UOH

LE002

10U0H

LE001

10U0H

FE001

47U0

CE022

DGND

DGND

47U0

CE041

CLAU_RST

+3V3SD

CLA_VID2

CLA_VID[0:7]

CLA_VID0

CLA_VID1

CLA_VID3

CLA_VID4

CLA_VID5

CLA_VID6

CLA_VID7

OSCLK/OSSTB

CLA_VID[0:7]

CLA_VCLKI

CLA_VCLKI

OSCLK/OSSTB

OSSYNC

+3V3SD

+3V3SD

CLAUDIA_33V

NE011

10K0

4

3

2

1

5

6

7

8

NE014

68R0

4

3

2

1

5

6

7

8

NE015

68R0

4

3

2

1

5

6

7

8

OS7

OS4

OS3

OS2

OS[0:7]

OS0

OS1

OS5

OS6

OSSYNC

0V5

ACLK

CA0

CA1

CA2

CA3

CA4

CA5

CCS

CD0

CD1

CD2

CD3

CD4

CD5

CD6

CD7

CIN/P7

CMODE0/CSL

CMODE1/CSDA/

CMODE2

CWAIT/CSROM

CWE/CSLA/CLDI

DCLK

DD0

DD1

DMS

DRE/CMODE3

DRSTZ

E85CLK

E85CLKSEL

ECLKSEL

FLDI

GND2-1

GND2-10

GND2-11

GND2-12

GND2-13

GND2-14

GND2-15

GND2-16

GND2-17

GND2-18

GND2-19

GND2-2

GND2-3

GND2-4

GND2-5

GND2-6

GND2-7

GND2-8

GND2-9

GND3-1

GND3-10

GND3-2

GND3-3

GND3-4

GND3-5

GND3-6

GND3-7

GND3-8

GND3-9

HSYNCI

IABCK

IABD

IALRCK

IISYNC

IS0

IS1

IS2

IS3

IS4

IS5

IS6

IS7

ISCK/ISSTB

ISSREQ

ISVLD

MA0

MA1

MA10

MA11

MA12

MA13

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MCAS

MCKE

MCLK

MCS

MD0

MD1

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD2

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD3

MD30

MD31

MD4

MD5

MD6

MD7

MD8

MD9

MDQM

MRAS

MWE

OABCK

OABD

OALRCK

OISYNC

OS0

OS1

OS2

OS3

OS4

OS5

OS6

OS7

OSREQ

OSSCK/OSSTB

OSVLD/OSRDY

OV0

OV1

OV2

OV3

OV4

OV6

OV7

P0/INTP0/TI11

P1/INTP1/TCLR1

P2/INTP2/TI12

P3/INTP3/TCLR2

P4/INTP4

P5/INTP5/HSYNCO

P6/INTP6/VSYNCO

PGND

PSTOP

PVDD2

PWM

RESET

SCLK

STCLK

TEST

VCLK

VCLK0

VDD2-1

VDD2-10

VDD2-11

VDD2-12

VDD2-13

VDD2-14

VDD2-15

VDD2-16

VDD2-17

VDD2-18

VDD2-19

VDD2-2

VDD2-3

VDD2-4

VDD2-5

VDD2-6

VDD2-7

VDD2-8

VDD2-9

VDD3-1

VDD3-10

VDD3-2

VDD3-3

VDD3-4

VDD3-5

VDD3-6

VDD3-7

VDD3-8

VDD3-9

VIN0

VIN1

VIN2

VIN3

VIN4

VIN5

VIN6

VIN7

VSYNCI

UPD61052

MPEG_ENCODER

21155940

IE001

207

208

205

206

141

116

105

100

94

93

96

97

98

95

83

84

85

81

82

80

76

75

73

78

77

74

72

71

70

66

65

68

67

61

53

52

50

36

11

1

20

9

8

7

6

5

4

19

18

3

17

16

15

14

13

12

10

2

21

22

23

24

25

30

29

28

27

26

31

32

33

34

35

40

39

38

37

41

42

43

44

45

49

48

47

46

51

54

55

58

59

57

56

63

64

62

60

79

69

86

87

89

88

91

92

90

99

101

104

103

102

106

108

107

110

109

114

115

112

113

111

119

120

117

118

124

125

122

123

121

129

130

127

128

126

134

135

132

133

131

139

140

137

138

136

144

145

142

143

149

150

147

148

146

154

155

152

153

151

156

204

200

199

197

198

201

202

203

190

189

187

188

185

184

186

193

192

191

195

194

176

174

175

171

172

173

180

179

177

178

181

182

183

163

162

161

158

157

159

160

166

164

165

168

167

169

170

196

RE014

68R0 68R0

RE015

RE016

68R0

ADSDATA1

IDR03_2ND_GEN

IE005 Pin1

IE005 Pin3

IE005 Pin9

IE005 Pin14

IE005 Pin27

IE005 Pin43

IE005 Pin49

IE003 Pin3

IE003 Pin9

IE003 Pin14

IE003 Pin27

IE003 Pin43

IE003 Pin49

IE003 Pin1

IE001 Pin186

IE001 Pin175

IE001 Pin163

IE001 Pin152

IE001 Pin140

IE001 Pin128

IE001 Pin105

IE001 Pin94

IE001 Pin82

IE001 Pin71

IE001 Pin60

IE001 Pin48

IE001 Pin36

IE001 Pin30

IE001 Pin24

IE001 Pin13

IE001 Pin1

IE001 Pin198

IE001 Pin117

IE001 Pin39

IE001 Pin69

IE001 Pin86

IE001 Pin98

IE001 Pin110

IE001 Pin122

IE001 Pin135

IE001 Pin171

IE001 Pin194

IE001 Pin148

1M X 16 X4

1M X 16 X4

External Clock Terminal

MPEG ENCODER

0R0

RE027

CLA_ACLK

0R0

RE043

IDR03 2ND GEN DIGITAL

MPEG ENCODER

MPEG

(DIGITAL BOARD 5/9)

MAIN SCHEMATIC DIAGRAM - SCHEMA DE LA PLATINE PRINCIPALE - SCHALTBILD HAUPTPLATINE - SCHEMA DELLA PIASTRA PRINCIPALE- ESQUEMA DE LA PLATINA PRINCIPAL