14

6

F

2

S

0

8

5

0

restraint. For details of the characteristic, see Section 2.16.

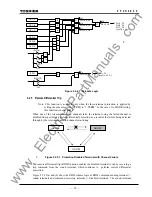

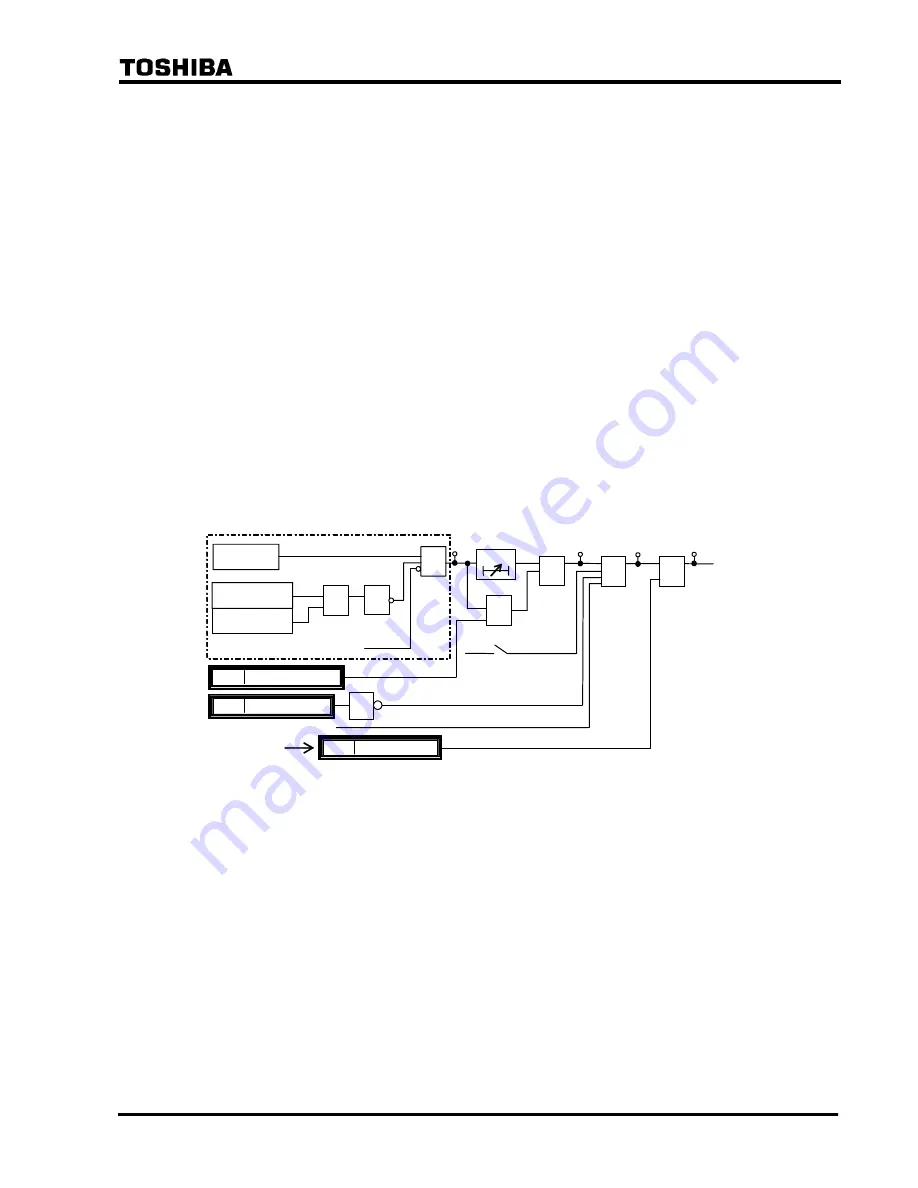

The scheme logic is shown in Figure 2.2.3.1. The output signal of the differential element DIFG

performs time-delayed three-phase tripping of the circuit breaker with the tripping output signal

DIFG.FS_TRIP. DIFG.FS_TRIP can start the incorporated autoreclose function when the

scheme switch [ARC-DIFG] is set to "ON". The DIFG can trip instantaneously by PLC

command DIFG_INST_TP.

Tripping output signal can be blocked by the PLC command DIFG_BLOCK and CRT_BLOCK.

The output signal is also blocked when a communication circuit failure is detected by data error

check, sampling synchronism check or interruption of the receive signals. For DIFG_FS signal,

see Section 2.2.4.

Since the DIFG is used for high-impedance earth fault protection, the DIFG output signal is

blocked when zero-phase current is large as shown in the following equation:

Σ

I

01

≥

2 pu or

Σ

I

02

≥

2 pu

where,

Σ

I

01

: Scalar summation of zero-phase current at local terminal relay

Σ

I

02

: Scalar summation of zero-phase current at remote terminal relay

pu: per unit value

In GPS-mode setting and backup mode (refer to 2.2.7.2), DIFG is blocked.

DIFG

DIFG.FS_TRIP

"ON"

&

1

Σ

I

01

≥

2PU

Σ

I

02

≥

2PU

≥

1

Communication failure, etc.

1

DIFG_BLOCK

1586

85

44

DIFG_FS

1619

&

404

43C ON

86

DIFG_TRIP

DIFGFS

DIFG_INST_TP

1632

≥

1

&

+

[DIFG]

t 0

TDIFG

0.0-10.0s

&

Figure 2.2.3.1 Scheme Logic of Zero-phase Current Differential Protection

2.2.4 Fail-safe

Function

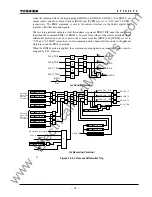

GRL100 provides OC1, OCD and EFD elements. These are used for fail-safe to prevent

unnecessary operation caused by error data in communication failure. OC1 is phase overcurrent

element and its sensitivity can be set. OCD is phase current change detection element, and EFD

is zero-sequence current change detection element. Both of the OCD and EFD sensitivities are

fixed. The scheme logic is shown in Figure 2.2.4.1.

The outputs of DIF.FS_OP and DIFG.FS_OP signals are connected to DIF-A_FS, DIF-B_FS,

DIF-C_FS and DIFG_FS respectively by PLC function. These are connected at the default

setting.

The fail-safe functions are disabled by [DIF-FS] and [DIFG-FS] switches. In the [DIF-FS], OC1

or OCD or both elements can be selected. If these switches are set to “OFF”, the signals of

DIF.FS_OP and DIFG.FS_OP are “1” and the fail-safe is disabled.

www

. ElectricalPartManuals

. com

Summary of Contents for GRL100-701B

Page 329: ... 328 6 F 2 S 0 8 5 0 w w w E l e c t r i c a l P a r t M a n u a l s c o m ...

Page 339: ... 338 6 F 2 S 0 8 5 0 w w w E l e c t r i c a l P a r t M a n u a l s c o m ...

Page 351: ... 350 6 F 2 S 0 8 5 0 w w w E l e c t r i c a l P a r t M a n u a l s c o m ...

Page 381: ... 380 6 F 2 S 0 8 5 0 w w w E l e c t r i c a l P a r t M a n u a l s c o m ...

Page 413: ... 412 6 F 2 S 0 8 5 0 w w w E l e c t r i c a l P a r t M a n u a l s c o m ...

Page 417: ... 416 6 F 2 S 0 8 5 0 w w w E l e c t r i c a l P a r t M a n u a l s c o m ...

Page 453: ... 452 6 F 2 S 0 8 5 0 w w w E l e c t r i c a l P a r t M a n u a l s c o m ...

Page 457: ... 456 6 F 2 S 0 8 5 0 w w w E l e c t r i c a l P a r t M a n u a l s c o m ...

Page 473: ...w w w E l e c t r i c a l P a r t M a n u a l s c o m ...