69

6

F

2

S

0

8

5

0

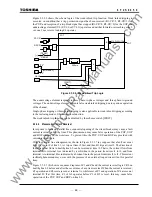

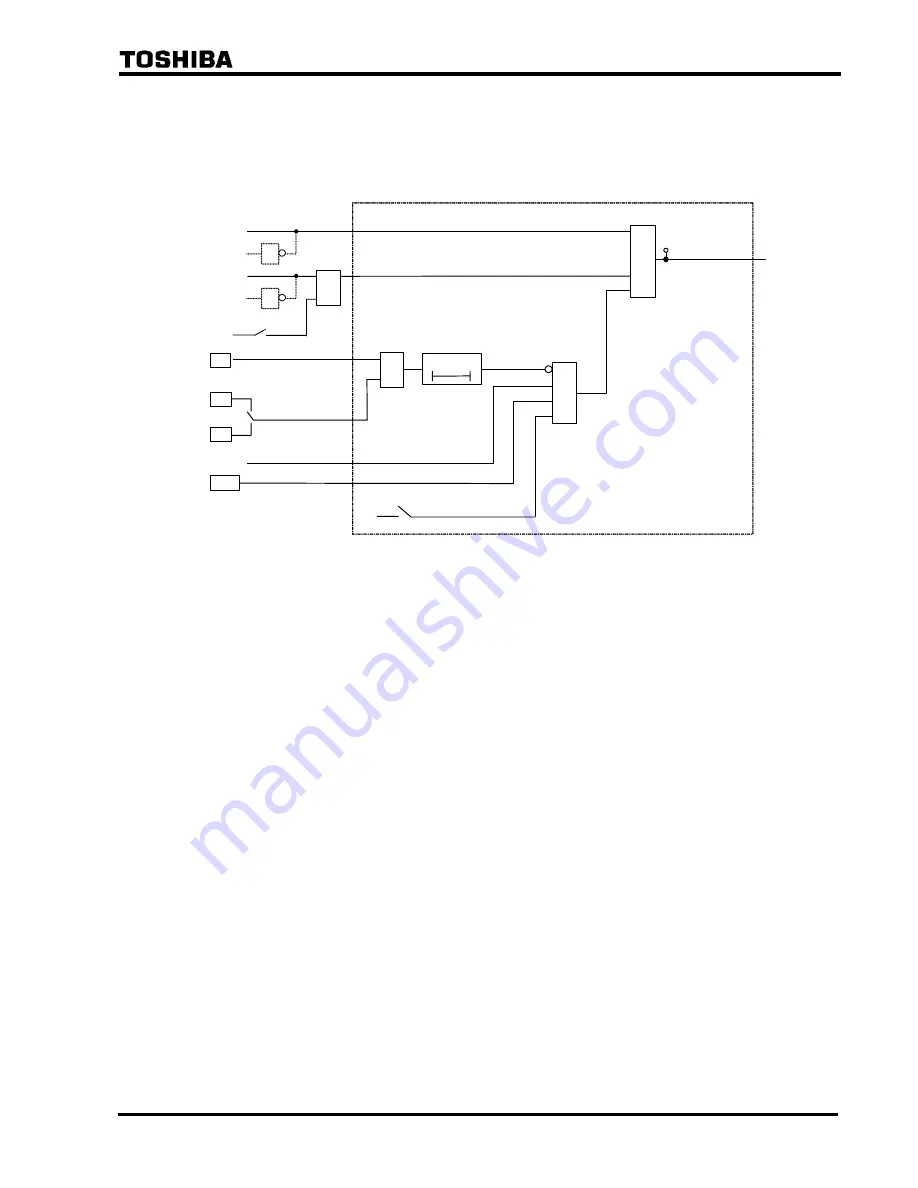

Figure 2.3.2.6 shows the scheme logic of the weak infeed trip function. Weak infeed tripping is

executed on condition that a trip permission signal has been received (R1-CR=1, R2-CR=1) for

the POP, and reception of a trip block signal has stopped (R1-CR=0, R2-CR=0) for the UOP, the

undervoltage element UVL (UVLS or UVLG) operates and neither forward overreaching zone 2

or zone 3 nor reverse looking Z4 operates.

WIT

&

WIT

[ZONESEL]

250ms

0 t

"Z3"

"Z2"

[WKIT]

"ON"

(+)

Z4

Z3

Z2

UVL

R2-CR

1

[

TERM

]

"2TERM"

(

+

)

≥

1

R1-CR

1

≥

1

&

CB-OR

876:DISWI_TRIP

Figure 2.3.2.6 Weak Infeed Trip Logic

The undervoltage element responds to three phase-to-phase voltages and three phase-to-ground

voltages. The undervoltage element prevents false weak infeed tripping due to spurious operation

of the channel.

Single-phase tripping or three-phase tripping is also applicable to weak infeed tripping according

to the reclosing mode of the autoreclose function.

The weak infeed trip function can be disabled by the scheme switch [WKIT].

2.3.2.6 Measure

for Current Reversal

In response to faults on parallel lines, sequential opening of the circuit breaker may cause a fault

current reversal on healthy lines. This phenomenon may cause false operation of the POP, UOP

and BOP schemes in the worst case. To prevent this, the POP, UOP and BOP are provided with

current reversal logic.

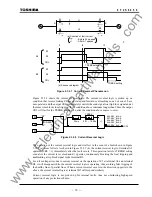

With the parallel line arrangement as shown in Figure 2.3.2.7 (a), suppose that a fault occurs at

time t1 at point F of line L1, A1 trips at time t2 first and then B1 trips at time t3. The direction of

the current that flows in healthy line L2 can be reversed at time t2. That is, the current flows from

terminal B to terminal A as indicated by a solid line in the period from time t1 to t2, and from

terminal A to terminal B as indicated by a broken line in the period from time t2 to t3. This current

reversal phenomenon may occur with the presence of an external looped circuit if not for parallel

lines.

Figure 2.3.2.7 (b) shows a sequence diagram of Z3 and Z4 and the current reversal logic CRL on

healthy line L2 before and after the occurrence of a current reversal. When the current is reversed,

Z3 operation and Z4 reset are seen at terminal A, while reset of Z3 and operation of Z4 are seen at

terminal B. If at this time, Z3 of A2 operates before Z3 of B2 is reset, this may cause false

operation of the POP, UOP and BOP on line L2.

www

. ElectricalPartManuals

. com

Summary of Contents for GRL100-701B

Page 329: ... 328 6 F 2 S 0 8 5 0 w w w E l e c t r i c a l P a r t M a n u a l s c o m ...

Page 339: ... 338 6 F 2 S 0 8 5 0 w w w E l e c t r i c a l P a r t M a n u a l s c o m ...

Page 351: ... 350 6 F 2 S 0 8 5 0 w w w E l e c t r i c a l P a r t M a n u a l s c o m ...

Page 381: ... 380 6 F 2 S 0 8 5 0 w w w E l e c t r i c a l P a r t M a n u a l s c o m ...

Page 413: ... 412 6 F 2 S 0 8 5 0 w w w E l e c t r i c a l P a r t M a n u a l s c o m ...

Page 417: ... 416 6 F 2 S 0 8 5 0 w w w E l e c t r i c a l P a r t M a n u a l s c o m ...

Page 453: ... 452 6 F 2 S 0 8 5 0 w w w E l e c t r i c a l P a r t M a n u a l s c o m ...

Page 457: ... 456 6 F 2 S 0 8 5 0 w w w E l e c t r i c a l P a r t M a n u a l s c o m ...

Page 473: ...w w w E l e c t r i c a l P a r t M a n u a l s c o m ...