98

6

F

2

S

0

7

8

9

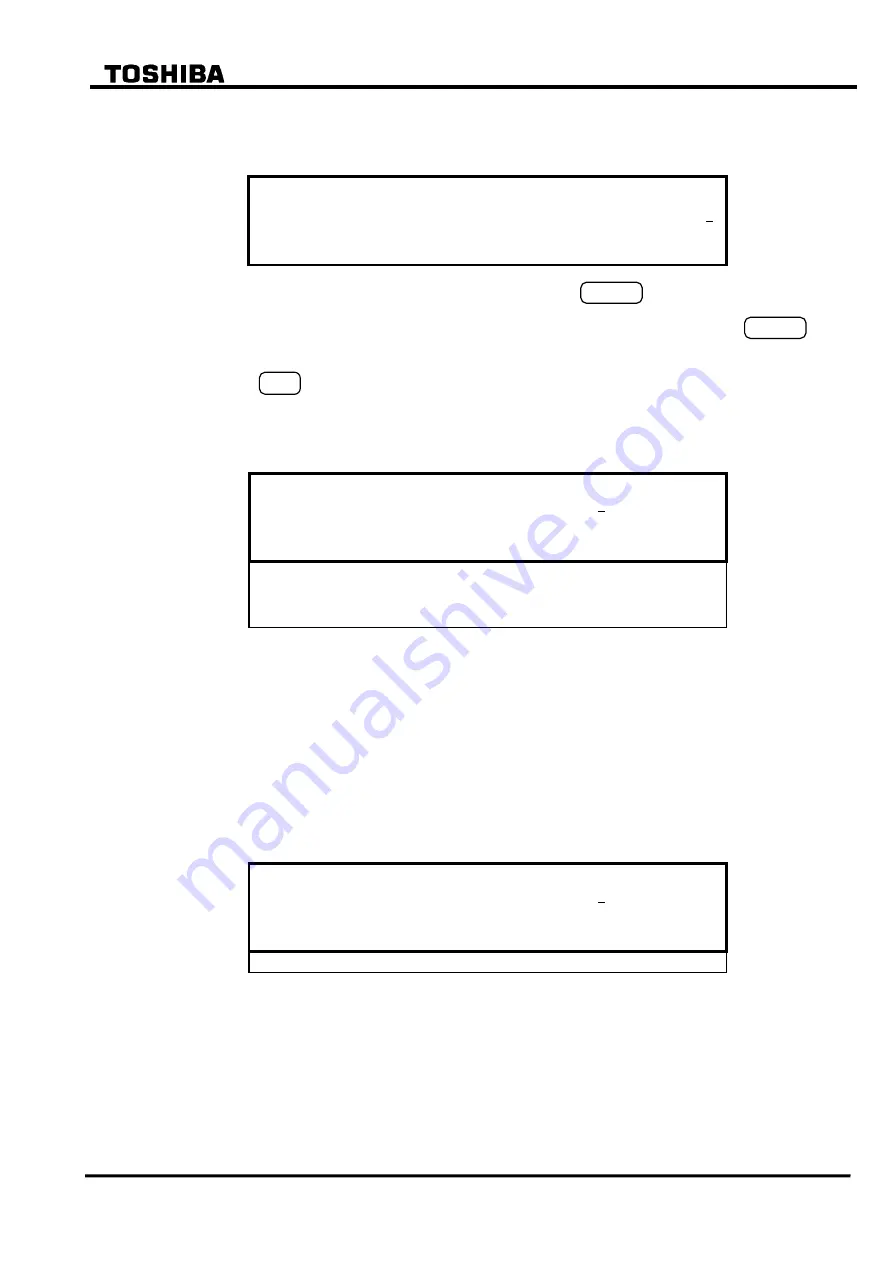

Setting the logic gate type and timer

Press 1 to display the "Logic gate type and delay timer" screen.

/ 5

L o g i c

g a t e

t y p e

&

d e l a y

t i m e r

1 /

2

L o g i c

1 = O R

2 = A N D

1

B O T D

0 = O f f 1 = O n

1

Enter 1 or 2 to use an OR gate or AND gate and press the

ENTER

key.

Enter 0 or 1 to add 0.2s drop-off delay time to the output relay or not and press the

ENTER

key.

Press the

END

key to return to the "Setting" screen.

Assigning signals

Press 2 on the "Setting" screen to display the "Input to logic gate" screen.

/ 5 I n p u t t o l o g i c g a t e

1 / 6

I n # 1 (

0 -

0 7 1 ) :

2 1

I n # 2 (

0 -

0 7 1 ) :

4

I n # 3 (

0 -

0 7 1 ) :

6 7

I n # 4 (

0 -

0 7 1 ) :

0

I n # 5 (

0 -

0 7 1 ) :

0

I n # 6 (

0 -

0 7 1 ) :

0

3

3

3

3

3

3

Assign signals to gates (In #1 to #6) by entering the number corresponding to each signal

referring to Appendix B.

Note:

If signals are not assigned to all the gates #1 to #6, enter 0 for the unassigned gate(s).

Repeat this process for the outputs to be configured.

4.2.6.10 LEDs

Four LEDs from bottom of the front panel are user-configurable. One of the signals listed in

Appendix B can be assigned to each LED as follows:

Press 9 (= LED) on the "Setting (change)" screen to display the "LED" screen.

/ 2 L E D

1 / 4

L E D 1 (

0 -

0 7 1 ) :

2 1

L E D 2 (

0 -

0 7 1 ) :

4

L E D 3 (

0 -

0 7 1 ) :

6 7

L E D 4 (

0 -

0 7 1 ) :

0

3

3

3

3

Enter the number corresponding to a signal to assign signals to each LED.

If an LED is not used, enter "0" or the default value will be assigned.

4.2.7 Testing

The sub-menu "Test" provides such functions as setting of testing switches, forced operation of

binary outputs, time measurement of the variable setting timer and logic signal observation.

Summary of Contents for GRT100 Series

Page 142: ... 141 6 F 2 S 0 7 8 9 Appendix A Block Diagram ...

Page 144: ... 143 6 F 2 S 0 7 8 9 Appendix B Signal List ...

Page 159: ... 158 6 F 2 S 0 7 8 9 ...

Page 160: ... 159 6 F 2 S 0 7 8 9 Appendix C Variable Timer List ...

Page 162: ... 161 6 F 2 S 0 7 8 9 Appendix D Binary Output Default Setting List ...

Page 165: ... 164 6 F 2 S 0 7 8 9 ...

Page 166: ... 165 6 F 2 S 0 7 8 9 Appendix E Details of Relay Menu and LCD and Button Operation ...

Page 174: ... 173 6 F 2 S 0 7 8 9 Appendix F Case Outline Flush Mount Type Rack Mount Type ...

Page 179: ... 178 6 F 2 S 0 7 8 9 ...

Page 180: ... 179 6 F 2 S 0 7 8 9 Appendix G External Connections ...

Page 185: ... 184 6 F 2 S 0 7 8 9 ...

Page 200: ... 199 6 F 2 S 0 7 8 9 ...

Page 201: ... 200 6 F 2 S 0 7 8 9 Appendix J Return Repair Form ...

Page 205: ... 204 6 F 2 S 0 7 8 9 Customer Name Company Name Address Telephone No Facsimile No Signature ...

Page 206: ... 205 6 F 2 S 0 7 8 9 ...

Page 207: ... 206 6 F 2 S 0 7 8 9 Appendix K Technical Data ...

Page 220: ... 219 6 F 2 S 0 7 8 9 ...

Page 221: ... 220 6 F 2 S 0 7 8 9 Appendix M Symbols Used in Scheme Logic ...

Page 224: ... 223 6 F 2 S 0 7 8 9 ...

Page 225: ... 224 6 F 2 S 0 7 8 9 Appendix N Implementation of Thermal Model to IEC60255 8 ...

Page 228: ... 227 6 F 2 S 0 7 8 9 ...

Page 229: ... 228 6 F 2 S 0 7 8 9 Appendix O IEC60870 5 103 Interoperability and Troubleshooting ...

Page 241: ... 240 6 F 2 S 0 7 8 9 Appendix P Modbus Interoperability ...

Page 255: ... 254 6 F 2 S 0 7 8 9 ...

Page 256: ... 255 6 F 2 S 0 7 8 9 Appendix Q Inverse Time Characteristics ...

Page 259: ... 258 6 F 2 S 0 7 8 9 ...

Page 260: ... 259 6 F 2 S 0 7 8 9 Appendix R Failed Module Tracing and Replacement ...

Page 266: ... 265 6 F 2 S 0 7 8 9 Appendix S Ordering ...

Page 269: ... 268 6 F 2 S 0 7 8 9 3 1 Oct 2 2017 Republished under spin off company ...

Page 270: ......