TC32306FTG

2015-10-01

43

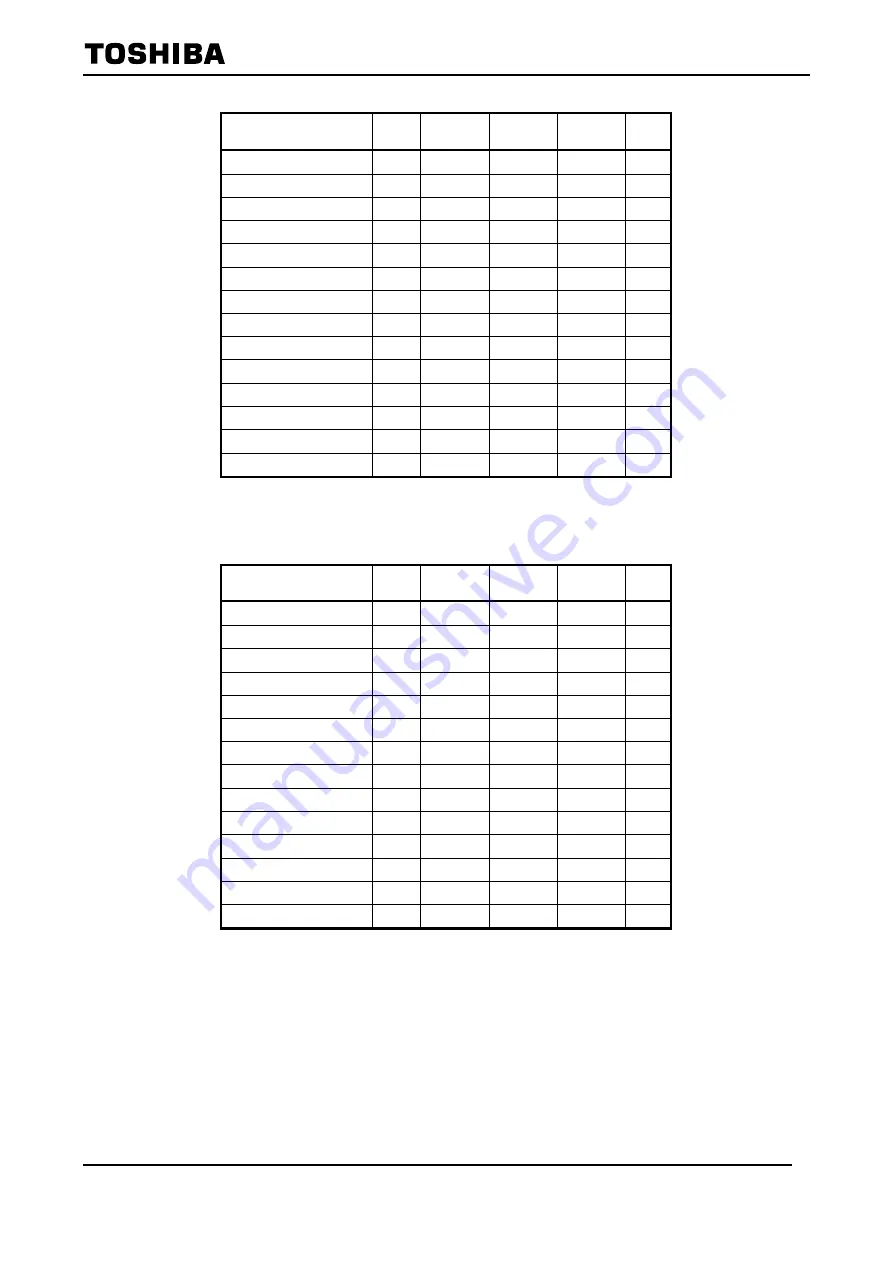

Table 6-41 EEPROM Mode Timing (COM_VDD = 3.0 - 5.5V)

Item

Code

Min

Typ.

Max

Unit

CLK Frequency *

f

ck

1.0

2.0

3.0

MHz

CLK ”H” Time *

t

CKWH

125

-

-

ns

CLK ”L” Time *

t

CKWL

125

-

-

ns

CLK Rising Time *

t

CKR

-

-

50

ns

CLK Falling Time *

t

CKF

-

-

50

ns

CLK Delay Time *

t

CKD

150

-

-

ns

CS Delay Time *

t

CSD

400

-

-

ns

CS “H” Time *

t

CSWH

500

-

-

ns

CS Hold Time *

t

CSH

100

-

-

ns

MOSI Preceding Time *

t

MOS

-

-

50

ns

MOSI Delay Time *

t

MOD

-

-

50

ns

MISO Delay Time

t

MID

-

-

90

ns

MISO Setup Time

t

MIS

-

-

10

ns

MISO Hold Time

t

MIH

-

-

100

ns

* Time values of CLK, MISO and MOSI are derived at the load capacitance of 10pF.

Table 6-42 EEPROM Mode Timing (COM_VDD = 2.5 - 3.0V)

Item

Code

Min

Typ.

Max

Unit

CLK Frequency *

f

ck

1.0

2.0

3.0

MHz

CLK ”H” Time *

t

CKWH

150

-

-

ns

CLK ”L” Time *

t

CKWL

150

-

-

ns

CLK Rising Time *

t

CKR

-

-

50

ns

CLK Falling Time *

t

CKF

-

-

50

ns

CLK Delay Time *

t

CKD

150

-

-

ns

CS Delay Time *

t

CSD

400

-

-

ns

CS “H” Time *

t

CSWH

500

-

-

ns

CS Hold Time *

t

CSH

100

-

-

ns

MOSI Preceding Time *

t

MOS

-

-

50

ns

MOSI Delay Time *

t

MOD

-

-

50

ns

MISO Delay Time

t

MID

-

-

120

ns

MISO Setup Time

t

MIS

-

-

10

ns

MISO Hold Time

t

MIH

-

-

100

ns

* Time values of CLK, MISO and MOSI are derived at the load capacitance of 10pF.

6.8 User Test

This is a mode to monitor internal digital signal for design, development, manufacturing or shipping

inspection. Set MODE1 pin to be “H” and/or the register: USER_TEST bit is “1” then TC32306FTG moves to

User Test. In User Test, various internal signals for the adjustment are converted to analog and are output

from DET_TMONI3 pin or DET_TMONI4 pin by the setting of register. The way of setting register of SPI

Mode is different from that of EEPROM Mode.