Chapter 6 Clocks

6-1

6. Clocks

6.1 TX4925

Clock

Signals

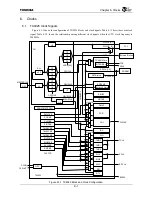

Figure 6.1.1 shows the configuration of TX4925 blocks and clock signals. Table 6.1.1 describes each clock

signal. Table 6.1.2 shows the relationship among different clock signals when the CPU clock frequency is

200 MHz.

Figure 6.1.1 TX4925 Block and Clock Configuration

SDCLK[1:0]

C32OUT

TCLK

PDNCTR.STPCPU

CLKCTR

TX4925

DMACKE

PCICKE

PIOCKE

TMR2CKE

TMR1CKE

TMR0CKE

SIO1CKE

CLKGATE

TMR2

TMR1

TMR0

SIO1

SIO0

SIO0CKE

SCLK

CHICKE

ACLC

SPI

RTC

BC32K

OSC

C32IN

ACLCKE

SPICKE

BITCLK

PCIC

IRC

PIO

CHI

CHICLK

MASTERCLK

OSC

CCFG.RF

CLKGATE

IMBUSCLKF

1/2

GBUSCLKF

1/2

IM

B

U

S

C

L

DMAC

EBUSC

NDFMC

1/8

SDRAMC

TX49/H2 Core

CPUCLK

GBUSCLK

CG

SYSCLK

SDCLKIN

PCICLK[2:1]

DATA latch

PLL

ADDR[4:3]

PCI

External Device

SDRAM

EJTAG/DSU

TCK

DCLK

1/6

Refresh Counter

1/1

1/2

1/4

1/8

x2.5

x4

1/1

1/2

1/4

1/1

1/2

1/3

1/4

PCICLK_IO

Summary of Contents for TMPR4925

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4925 Rev 3 0 ...

Page 4: ......

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4925 ...

Page 44: ......

Page 54: ...Chapter 1 Features 1 8 ...

Page 58: ...Chapter 2 Block Diagram 2 4 ...

Page 88: ...Chapter 4 Address Mapping 4 12 ...

Page 226: ...Chapter 8 DMA Controller 8 58 ...

Page 260: ...Chapter 9 SDRAM Controller 9 34 ...

Page 480: ...Chapter 15 Interrupt Controller 15 32 ...

Page 554: ...Chapter 19 Real Time Clock RTC 19 8 ...

Page 555: ...Chapter 20 Removed 20 1 20 Removed ...

Page 556: ...Chapter 20 Removed 20 2 ...

Page 564: ...Chapter 21 Extended EJTAG Interface 21 8 ...

Page 580: ...Chapter 22 Electrical Characteristics 22 16 ...

Page 588: ...Chapter 24 Usage Notes 24 2 ...