Chapter 7 External Bus Controller

7-6

7.3.4 External

Address

Output

The maximum memory space size for each channel is 1 GB (230B). Addresses are output by dividing

the 20-bit ADDR[19:0] signal into two parts: the upper address and the lower address. The address bit

output to each bit of the ADDR[19:0] signal changes according to the setting of the channel data bus

width. (See “7.3.5 Data Bus Size” for more information.)

It is possible for an external device to latch the upper eight address bits using the UAE signal. Either

the UAE signal itself can be used as a Latch Enable signal or the upper address can be latched at the rise

of SYSCLK when the UAE signal is being asserted.

The ADDR signal output is held for one clock cycle after the UAE signal assertion when the

CCFG.UAEHOLD bit is set (default). (See Figure 7.5.1.) The ADDR signal output is not held when the

CCFG.UAEHOLD bit is cleared. This hold time setting is applied globally to all channels.

The UAE signal of the upper address is always asserted at the first external bus access cycle after

Reset. In all subsequent external bus access cycles, the bit mapping of the upper address output to

ADDR[19:12] is compared to the bit mapping of the upper address output to ADDR[19:12] previously.

The upper address is output and the UAE signal is asserted only if the compared results do not match.

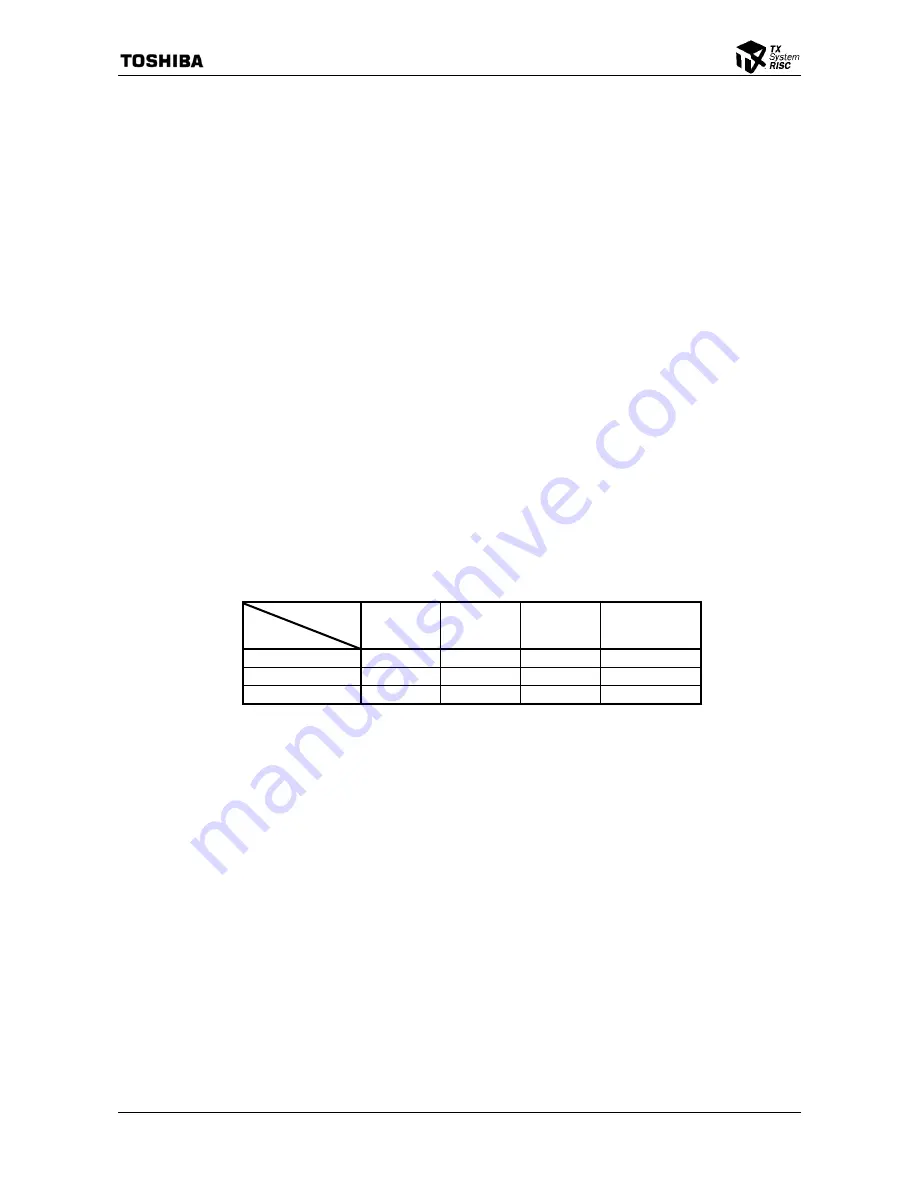

As indicated below in Table 7.3.3, in the case of channel sizes that do not use the upper address

latched by the UAE signal, with the exception of the first cycle after reset, the upper address is not

output and the UAE signal is not asserted.

Table 7.3.3 Relationship Between the Upper Address Output and the Channel Size (CS)

CS

Bus Width

1 MB

2 MB

4 MB

8 MB or more

32 bits

⎯

⎯

⎯

√

16 bits

⎯

⎯

√

√

8 bits

⎯

√

√

√

√

: The upper address output changes when the upper address changes.

⎯

: The upper address output does not change (with the exception of the first cycle after

reset.)

Summary of Contents for TMPR4925

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4925 Rev 3 0 ...

Page 4: ......

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4925 ...

Page 44: ......

Page 54: ...Chapter 1 Features 1 8 ...

Page 58: ...Chapter 2 Block Diagram 2 4 ...

Page 88: ...Chapter 4 Address Mapping 4 12 ...

Page 226: ...Chapter 8 DMA Controller 8 58 ...

Page 260: ...Chapter 9 SDRAM Controller 9 34 ...

Page 480: ...Chapter 15 Interrupt Controller 15 32 ...

Page 554: ...Chapter 19 Real Time Clock RTC 19 8 ...

Page 555: ...Chapter 20 Removed 20 1 20 Removed ...

Page 556: ...Chapter 20 Removed 20 2 ...

Page 564: ...Chapter 21 Extended EJTAG Interface 21 8 ...

Page 580: ...Chapter 22 Electrical Characteristics 22 16 ...

Page 588: ...Chapter 24 Usage Notes 24 2 ...