Chapter 10 PCI Controller

10-5

Registers in the PCI Controller Control Register that include an offset address in the range from

0xD000 to 0xD07F can only be accessed when in the Host mode and cannot be accessed when in the

Satellite mode. These registers correspond to PCI Configuration Space Registers that an external PCI

Host device accesses when in the Satellite mode. Section 10.4 “PCI Controller Control Register”

explains each register in detail.

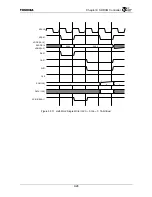

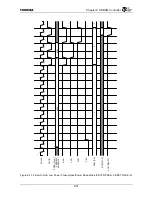

Figure 10.3.1illustrates the register map when in the Host mode. Figure 10.3.2 illustrates the register

map when in the Satellite mode.

Figure 10.3.1 Register Map in the Host Mode

Figure 10.3.2 Register Map in the Satellite Mode

PCI Controller Control Register

Reserved

Reserved

G-Bus Address Space

PCI Bus Configuration Space

0xDFFF

0xD270

0xD000

0x00

0x80

0xFF

PCI Controller

Control Register

PCI Configuration

Space Register

Reserved

G-Bus Address Space

PCI Bus Configuration Space

0xDFFF

0xD270

0xD000

0x00

0x60

0xFF

Reserved

0xD060

Reserved

0xd0

0xD0d0

0xD100

Summary of Contents for TMPR4925

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4925 Rev 3 0 ...

Page 4: ......

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4925 ...

Page 44: ......

Page 54: ...Chapter 1 Features 1 8 ...

Page 58: ...Chapter 2 Block Diagram 2 4 ...

Page 88: ...Chapter 4 Address Mapping 4 12 ...

Page 226: ...Chapter 8 DMA Controller 8 58 ...

Page 260: ...Chapter 9 SDRAM Controller 9 34 ...

Page 480: ...Chapter 15 Interrupt Controller 15 32 ...

Page 554: ...Chapter 19 Real Time Clock RTC 19 8 ...

Page 555: ...Chapter 20 Removed 20 1 20 Removed ...

Page 556: ...Chapter 20 Removed 20 2 ...

Page 564: ...Chapter 21 Extended EJTAG Interface 21 8 ...

Page 580: ...Chapter 22 Electrical Characteristics 22 16 ...

Page 588: ...Chapter 24 Usage Notes 24 2 ...