Chapter 10 PCI Controller

10-10

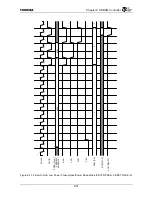

Table 10.3.3 Initiator Access Space Properties Register

Enable

Word

Swap

Memory Space 0

BusMasterEnable

& G2PCFG.G2PM0EN

G2PCFG.BSWAPM0

Memory Space 1

BusMasterEnable

& G2PCFG.G2PM1EN

G2PCFG.BSWAPM1

Memory Space 2

BusMasterEnable

& G2PCFG.G2PM2EN

G2PCFG.BSWAPM2

I/O Space

BusMasterEnable

& G2PCFG.G2PIOEN

G2PCFG.BSWAPIO

BusMasterEnable

:

Host mode:

PCI State Command Register Bus Master Bit (PCISTATUS.BM)

Satellite mode: Command Register Bus Master bit

10.3.5 Target

Access

(PCI

Bus

→

G-Bus Address Conversion)

During PCI target access, the PCI Bus address of the Bus transaction issued by the PCI Bus is

converted into a G-Bus address and is used to issue a Bus transaction on the G-Bus. 32-bit PCI Bus

addresses are used on the PCI Bus. Also, 32-bit physical addresses are used on the G-Bus.

Three memory access windows and one I/O access window can be set in the PCI bus space (Figure

10.3.5). The size of each memory window is variable from 1 MByte to 512 MBytes. The size of the I/O

windo is variable from 256 Bytes to 64 Kbytes. When Bus transactions to these access windows is

issued on the PCI Bus, these Bus transactions are accepted as PCI target devices. The PCI Bus Address

is converted into G-Bus addresses, then Bus transactions are issued to the G-Bus.

The memory space window responds to the PCI memory space access command. The I/O space

window responds to the PCI I/O space access command.

Figure 10.3.5 Target Access Memory Window

Memory Access Window

I/O Access Window

0x00_0000_0000

0xFFFF_FFFF

0x0000_0000

0x00_0000_0000

0xFFFF_FFFF

0xFFFF_FFFF

PCI I/O Space

G-Bus Space

PCI Memory Space

Summary of Contents for TMPR4925

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4925 Rev 3 0 ...

Page 4: ......

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4925 ...

Page 44: ......

Page 54: ...Chapter 1 Features 1 8 ...

Page 58: ...Chapter 2 Block Diagram 2 4 ...

Page 88: ...Chapter 4 Address Mapping 4 12 ...

Page 226: ...Chapter 8 DMA Controller 8 58 ...

Page 260: ...Chapter 9 SDRAM Controller 9 34 ...

Page 480: ...Chapter 15 Interrupt Controller 15 32 ...

Page 554: ...Chapter 19 Real Time Clock RTC 19 8 ...

Page 555: ...Chapter 20 Removed 20 1 20 Removed ...

Page 556: ...Chapter 20 Removed 20 2 ...

Page 564: ...Chapter 21 Extended EJTAG Interface 21 8 ...

Page 580: ...Chapter 22 Electrical Characteristics 22 16 ...

Page 588: ...Chapter 24 Usage Notes 24 2 ...