Chapter 11 Serial I/O Port

11-12

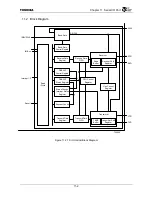

11.3.12 Multi-Controller System

The Multi-Controller System consists of one Master Controller, and multiple Slave Controllers as

shown below in Figure 11.3.4.

In the case of the Multi-Controller System, the Master Controller transmits an address (ID) frame to

all Slave Controllers, then transmits and receives data with the selected Slave Controller. Slave

Controllers that were not selected will ignore this data.

Data frames whose data frame Wake Up bits (WUB) are “1” are handled as address (ID) frames. Data

frames whose Wake Up bit (WUB) is “0” are handled as data frames.

Figure 11.3.4 Example Configuration of Multi-Controller System

The data transfer procedure for the Multi-Controller System is as follows.

(1) The Master and Slave Controllers set the Mode field (UMODE) of the Line Control Register

(SILCR) to “10” or “11” to set the Multi-Controller System mode. Also, the Slave Controller sets

the open drain enable bit (UODE) of the Line Control Register (SILCR), setting the TXD output

signal to open drain output.

(2) The Slave Controller sets the Reception Wake Up bit (RWUB) of the Line Control Register

(SILCR), making it possible to receive address (ID) frames from the Master Controller.

(3) The Master Controller sets the Transmission Wake Up bit (TWUB) of the Line Control Register

(SILCR), and transmits the address (ID) of the selected Slave Controller. This causes the address

(ID) frame to be transmitted. The Reception after Address Transmission Wake Up bit (RWUB) is

cleared, enabling reception of data frames.

(4) Since the Reception Wake Up bit (RWUB) is set, the Slave Controller generates an interrupt to the

CPU by receiving an address (ID) frame. The CPU compares its own address (ID) and the received

data together. If they match, the Reception Wake Up bit (RWUB) is cleared, making data frame

reception possible.

(5) The Master Controller and the selected Slave Controller clear the Transmission Wake Up bit

(TWUB) of the Line Control Register (SILCR), then set the mode that transmits data frames.

(6) Transmit/Receive data between the Master Controller and the selected Slave Controller. Then,

Slave Controllers that were not selected ignore data frames since the Reception Wake Up bit

(RWUB) is still set.

RXD TXD

Slave #3

RXD TXD

Slave #2

RXD TXD

Slave #1

Master

TXD RXD

Summary of Contents for TMPR4925

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4925 Rev 3 0 ...

Page 4: ......

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4925 ...

Page 44: ......

Page 54: ...Chapter 1 Features 1 8 ...

Page 58: ...Chapter 2 Block Diagram 2 4 ...

Page 88: ...Chapter 4 Address Mapping 4 12 ...

Page 226: ...Chapter 8 DMA Controller 8 58 ...

Page 260: ...Chapter 9 SDRAM Controller 9 34 ...

Page 480: ...Chapter 15 Interrupt Controller 15 32 ...

Page 554: ...Chapter 19 Real Time Clock RTC 19 8 ...

Page 555: ...Chapter 20 Removed 20 1 20 Removed ...

Page 556: ...Chapter 20 Removed 20 2 ...

Page 564: ...Chapter 21 Extended EJTAG Interface 21 8 ...

Page 580: ...Chapter 22 Electrical Characteristics 22 16 ...

Page 588: ...Chapter 24 Usage Notes 24 2 ...