Chapter 12 Timer/Counter

12-11

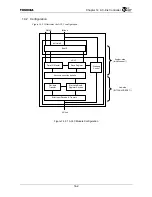

12.4.2 Timer Interrupt Status Register

n

(TMTISRn)

TMTISR0

0xF004

TMTISR1

0xF104

TMTISR2

0xF204

31

16

0

:

Type

: Initial value

15

4

3

2

1

0

0 TWIS TPIBS

TPIAS

TIIS

R/W0C R/W0C

R/W0C

R/W0C :

Type

0

0

0

0

:

Initial

value

Bits Mnemonic Field

Name

Description

31:4

⎯

Reserved

⎯

3 TWIS

Watchdog Timer

Status

Watchdog Timer TMCPRA Match Status (Initial value: 0, R/W0C)

(This bit is Reserved in the case of the TMTISR0 Register and the TMTISR1 Register.)

When in the Watchdog Timer mode, this bit is set when the counter value matches

Compare Register 2 (TMCPRA2).

This bit is cleared by writing a “0” to it.

During Read

0: Did not match the Compare Register

1: Matched the Compare Register

During Write

0: Negate interrupt

1: Invalid

2 TPIBS

Pulse Generator

TMCPRB Status

Pulse Generator TMCPRB Match Status (Initial value: 0, R/W0C)

(This bit is Reserved in the case of the TMTISR2 Register.)

When in the Pulse Generator mode, this bit is set when the counter value matches

Compare Register Bn (TMCPRBn).

This bit is cleared by writing a “0” to it.

During Read

0: Did not match the Compare Register

1: Matched the Compare Register

During Write

0: Clear

1: Invalid

1 TPIAS

Pulse Generator

TMCPRA Status

Pulse Generator TMCPRA Match Status (Initial value: 0, R/W0C)

(This bit is Reserved in the case of the TMTISR2 Register.)

When in the Pulse Generator mode, this bit is set when the counter value matches

Compare Register A n (TMCPRAn).

This bit is cleared by writing a “0” to it.

During Read

0: Did not match the Compare Register

1: Matched the Compare Register

During Write

0: Clear

1: Invalid

0 TIIS

Interval Timer

TMCPRA Status

Interval Timer TMCPRA Match Status (Initial value: 0, R/W0C)

When in the Interval Timer mode, this bit is set when the counter value matches

Compare Register A n (TMCPRAn).

This bit is cleared by writing a “0” to it.

During Read

0: Did not match the Compare Register

1: Matched the Compare Register

During Write

0: Clear

1: Invalid

Figure 12.4.2 Timer Interrupt Status Register

Summary of Contents for TMPR4925

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4925 Rev 3 0 ...

Page 4: ......

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4925 ...

Page 44: ......

Page 54: ...Chapter 1 Features 1 8 ...

Page 58: ...Chapter 2 Block Diagram 2 4 ...

Page 88: ...Chapter 4 Address Mapping 4 12 ...

Page 226: ...Chapter 8 DMA Controller 8 58 ...

Page 260: ...Chapter 9 SDRAM Controller 9 34 ...

Page 480: ...Chapter 15 Interrupt Controller 15 32 ...

Page 554: ...Chapter 19 Real Time Clock RTC 19 8 ...

Page 555: ...Chapter 20 Removed 20 1 20 Removed ...

Page 556: ...Chapter 20 Removed 20 2 ...

Page 564: ...Chapter 21 Extended EJTAG Interface 21 8 ...

Page 580: ...Chapter 22 Electrical Characteristics 22 16 ...

Page 588: ...Chapter 24 Usage Notes 24 2 ...