Chapter 14 AC-link Controller

14-16

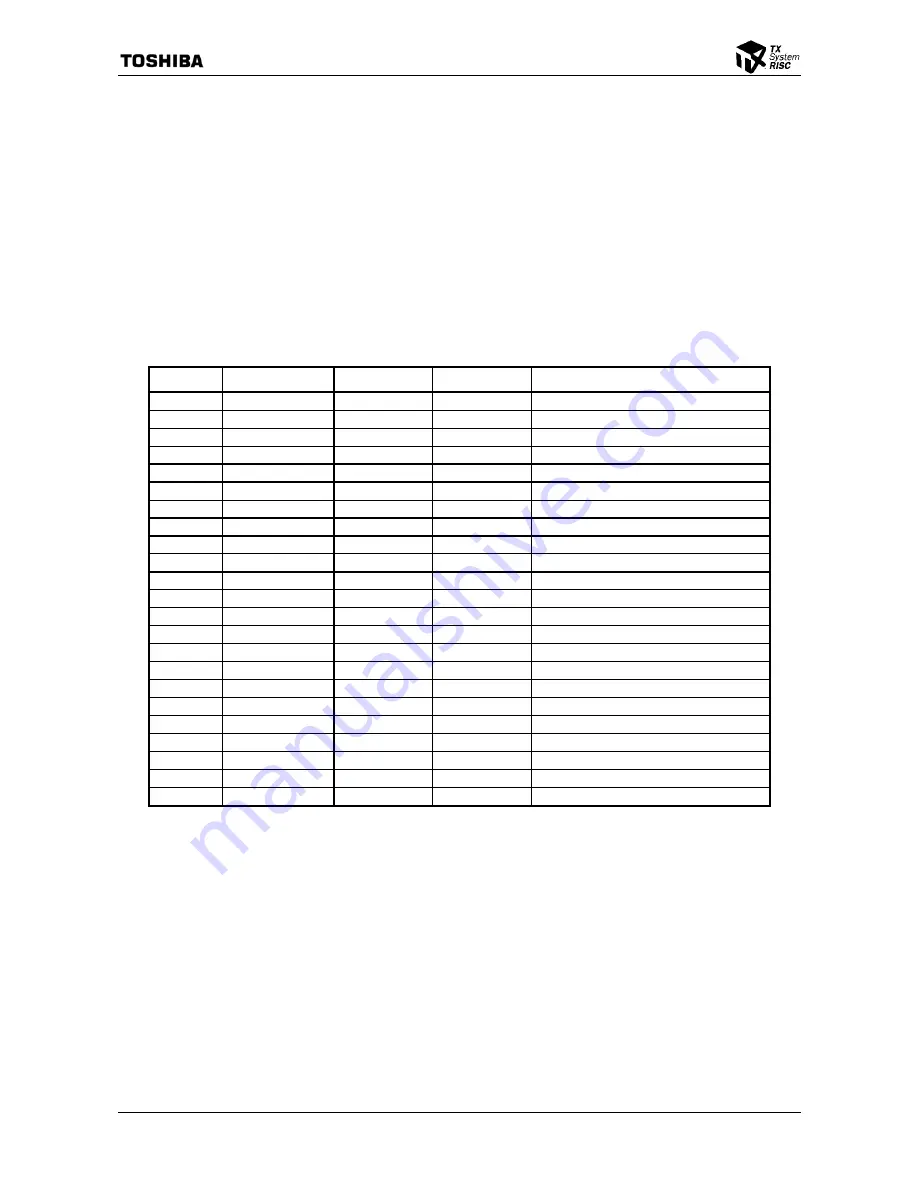

14.4 Registers

The base address for the ACLC registers is described in section 5.1.7. Only word (32-bit) accesses are

allowed. These registers return to their initial values when the module gets reset by power-on or

configuration-register operation. The ‘Disable AC-link’ operation initializes the ACREGACC, ACGPIDAT,

ACGPODAT, and ACSLTEN registers while keeping the other registers.

Do not access any location which is not mentioned in this section.

All the register bits marked as ‘Reserved’ are reserved. The value of the reserved bit when read is

undefined. When any register is written, write to the reserved bit(s) the same value as the previous value

read.

Table 14.4.1 ACLC Registers

Reference Offset

Address

Bit

Width

Mnemonic

Register

Name

14.4.1

0xF700

32

ACCTLEN

ACLC Control Enable Register

14.4.2

0xF704

32

ACCTLDIS

ACLC Control Disable Register

14.4.3

0xF708

32

ACREGACC

ACLC CODEC Register Access Register

14.4.4

0xF710

32

ACINTSTS

ACLC Interrupt Status Register

14.4.5

0xF714

32

ACINTMSTS

ACLC Interrupt Masked Status Register

14.4.6

0xF718

32

ACINTEN

ACLC Interrupt Enable Register

14.4.7

0xF71C

32

ACINTDIS

ACLC Interrupt Disable Register

14.4.8

0xF720

32

ACSEMAPH

ACLC Semaphore Register

14.4.9

0xF740

32

ACGPIDAT

ACLC GPI Data Register

14.4.10

0xF744

32

ACGPODAT

ACLC GPO Data Register

14.4.11

0xF748

32

ACSLTEN

ACLC Slot Enable Register

14.4.12

0xF74C

32

ACSLTDIS

ACLC Slot Disable Register

14.4.13

0xF750

32

ACFIFOSTS

ACLC FIFO Status Register

14.4.14

0xF780

32

ACDMASTS

ACLC DMA Request Status Register

14.4.15

0xF784

32

ACDMASEL

ACLC DMA Channel Selection Register

14.4.16

0xF7A0

32

ACAUDODAT

ACLC Audio PCM Output Data Register

14.4.16

0xF7A4

32

ACSURRDAT

ACLC Surround Data Register

14.4.17

0xF7A8

32

ACCENTDAT

ACLC Center Data Register

14.4.17

0xF7AC

32

ACLFEDAT

ACLC LFE Data Register

14.4.18

0xF7B0

32

ACAUDIDAT

ACLC Audio PCM Input Data Register

14.4.17

0xF7B8

32

ACMODODAT

ACLC Modem Output Data Register

14.4.19

0xF7BC

32

ACMODIDAT

ACLC Modem Input Data Register

14.4.20

0xF7FC

32

ACREVID

ACLC Revision ID Register

Summary of Contents for TMPR4925

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4925 Rev 3 0 ...

Page 4: ......

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4925 ...

Page 44: ......

Page 54: ...Chapter 1 Features 1 8 ...

Page 58: ...Chapter 2 Block Diagram 2 4 ...

Page 88: ...Chapter 4 Address Mapping 4 12 ...

Page 226: ...Chapter 8 DMA Controller 8 58 ...

Page 260: ...Chapter 9 SDRAM Controller 9 34 ...

Page 480: ...Chapter 15 Interrupt Controller 15 32 ...

Page 554: ...Chapter 19 Real Time Clock RTC 19 8 ...

Page 555: ...Chapter 20 Removed 20 1 20 Removed ...

Page 556: ...Chapter 20 Removed 20 2 ...

Page 564: ...Chapter 21 Extended EJTAG Interface 21 8 ...

Page 580: ...Chapter 22 Electrical Characteristics 22 16 ...

Page 588: ...Chapter 24 Usage Notes 24 2 ...