Chapter 16 CHI Module

16-26

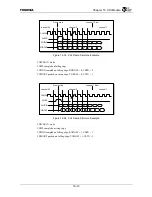

16.4.6 CHI Transmit Pointer B Register (TXPTRB)

0xA814

31 29

28 24

23 21

20 16

Reserved TXPTRB3 Reserved

TXPTRB2

W W

:

Type

00000 00000

:

Initial

value

15 13

12 8 7 5 4 0

Reserved TXPTRB1 Reserved

TXPTRB0

W W

:

Type

00000 00000

:

Initial

value

Bits Mnemonic Field

Name

Description

31:29

⎯

Reserved

⎯

28:24

TXPTRB3[4:0]

CHITXPTRB3

CHITXPTRB3 bits (Initial value: 00000, W)

These bits represent the TDM switch pointer which defines the transmit channel

timeslot for byte 3 of the CHI transmit holding register B; register B handles all

timeslots from channel (CHINCHAN

+

1) to channel (CHINCHAN

×

2

+

1). The

value loaded for this TDM switch pointer is the desired timeslot number minus

(CHINCHAN

+

1).

23:21

⎯

Reserved

⎯

20:16

TXPTRB2[4:0]

CHITXPTRB2

CHITXPTRB2 bits (Initial value: 00000, W)

These bits represent the TDM switch pointer which defines the transmit channel

timeslot for byte 2 of the CHI transmit holding register B; register B handles all

timeslots from channel (CHINCHAN

+

1) to channel (CHINCHAN

×

2

+

1). The

value loaded for this TDM switch pointer is the desired timeslot number minus

(CHINCHAN

+

1).

15:13

⎯

Reserved

⎯

12:8

TXPTRB1[4:0]

CHITXPTRB1

CHITXPTRB1 bits (Initial value: 00000, W)

These bits represent the TDM switch pointer which defines the transmit channel

timeslot for byte 1 of the CHI transmit holding register B; register B handles all

timeslots from channel (CHINCHAN

+

1) to channel (CHINCHAN

×

2

+

1). The

value loaded for this TDM switch pointer is the desired timeslot number minus

(CHINCHAN

+

1).

7:5

⎯

Reserved

⎯

4:0

TXPTRB0[4:0]

CHITXPTRB0

CHITXPTRB0 bits (Initial value: 00000, W)

These bits represent the TDM switch pointer which defines the transmit channel

timeslot for byte 0 of the CHI transmit holding register B; register B handles all

timeslots from channel (CHINCHAN

+

1) to channel (CHINCHAN

×

2

+

1). The

value loaded for this TDM switch pointer is the desired timeslot number minus

(CHINCHAN

+

1).

Figure 16.4.6 CHI Transmit Pointer B Register (TXPTRB)

Summary of Contents for TMPR4925

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4925 Rev 3 0 ...

Page 4: ......

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4925 ...

Page 44: ......

Page 54: ...Chapter 1 Features 1 8 ...

Page 58: ...Chapter 2 Block Diagram 2 4 ...

Page 88: ...Chapter 4 Address Mapping 4 12 ...

Page 226: ...Chapter 8 DMA Controller 8 58 ...

Page 260: ...Chapter 9 SDRAM Controller 9 34 ...

Page 480: ...Chapter 15 Interrupt Controller 15 32 ...

Page 554: ...Chapter 19 Real Time Clock RTC 19 8 ...

Page 555: ...Chapter 20 Removed 20 1 20 Removed ...

Page 556: ...Chapter 20 Removed 20 2 ...

Page 564: ...Chapter 21 Extended EJTAG Interface 21 8 ...

Page 580: ...Chapter 22 Electrical Characteristics 22 16 ...

Page 588: ...Chapter 24 Usage Notes 24 2 ...