Chapter 8 DMA Controller

8-26

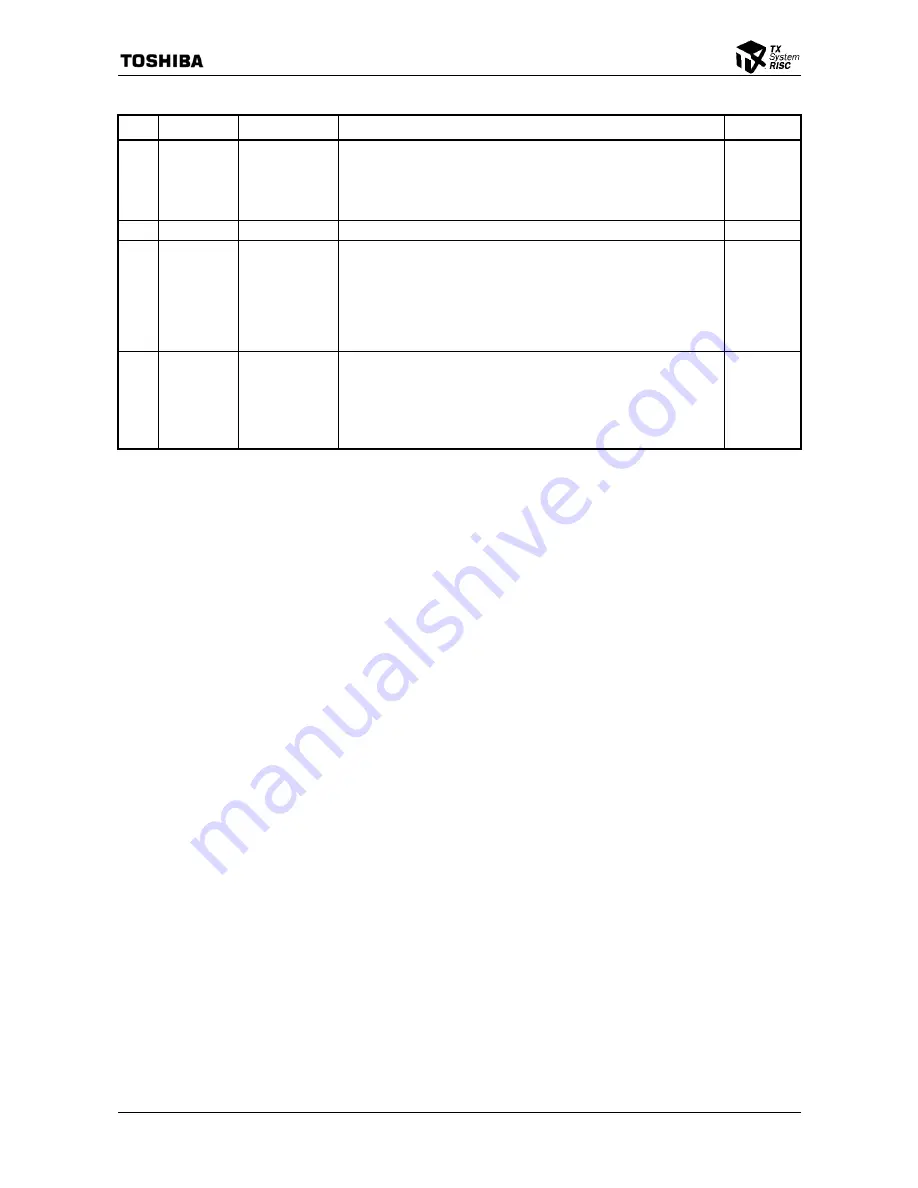

Bit Mnemonic Field

Name

Description Read/Write

6:3 FIFUM[3:0]

FIFO Use Enable

[3:0]

FIFO Use Enable [3:0] (Default: 0x0)

Each channel specifies whether to use 8-double word FIFO in Dual

Address transfer. FIFUM[n] corresponds to channel

n

.

Refer to “8.3.8.2 Burst Transfer During Dual Address Transfer” for more

information.

R/W

2

Reserved

⎯

1 RRPT

Round Robin

Priority

Round Robin Priority (Default: 0)

Specifies the method for determining priority among channels.

1: Round Robin method. Priority of the last channel used is the lowest,

and the next previous channel has the next lowest priority. Round robin

is in the order Channel 0 > Channel 1 > Channel > Channel 3.

0: Fixed Priority. Priority is fixed in the order Channel 0 > Channel 1 >

Channel 2 > Channel 3.

R/W

0 MSTEN

Master

Enable Master Enable (Default: 0)

This bit enables the DMA Controller.

1: Enable

0: Disable

Note: If the entire DMA Controller is disabled, then all internal logic

including the Bus Interface Logic and State Machine are reset.

R/W

Figure 8.4.1 DMA Master Control Register (2/2)

Summary of Contents for TX49 TMPR4937

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Page 4: ......

Page 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Page 14: ...Table of Contents x ...

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4937 2005 3 Rev 2 0 ...

Page 44: ......

Page 52: ...Chapter 1 Overview and Features 1 6 ...

Page 156: ...Chapter 7 External Bus Controller 7 56 ...

Page 491: ...Chapter 16 Removed 16 1 16 Removed ...

Page 492: ...Chapter 16 Removed 16 2 ...

Page 493: ...Chapter 17 Removed 17 1 17 Removed ...

Page 494: ...Chapter 17 Removed 17 2 ...

Page 495: ...Chapter 18 Removed 18 1 18 Removed ...

Page 496: ...Chapter 18 Removed 18 2 ...

Page 497: ...Chapter 19 Removed 19 1 19 Removed ...

Page 498: ...Chapter 19 Removed 19 2 ...

Page 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

Page 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Page 542: ...Chapter 24 Parts Number when Ordering 24 2 ...