Chapter 8 DMA Controller

8-32

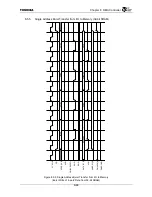

Bit Mnemonic Field

Name

Description Read/Write

8

XFACT

Transfer Active

Transfer Active (Default: 0)

This value is a copy of the Transfer Active bit (XFACT) of the DMA

Channel Control Register (DMCCRn).

R

7

ABCHC

Error Complete

Error Completion (Default: 0)

This bit indicates whether an error occurred during DMA transfer. This bit

indicates the logical sum of the four error bits (CFERR, CHERR, DESERR,

SORERR) in DMCSRn[3:0].

1: DMA transfer ends due to an error.

0: No error occurred since this bit was last cleared.

R

6

NCHNC

Chain Complete

Normal Chain Completion (Default: 0)

When performing chain DMA transfer, This bit indicates whether all DMA

data transfers in the DMA Descriptor chain are complete.

1: All DMA data transfers in the DMA Descriptor chain ended normally. Or,

DMA transfer that did not use a DMA Descriptor chain ended normally.

0: DMA transfer has not ended normally since this bit was last cleared.

R/W1C

5 NTRNFC

Transfer

Complete

Normal Transfer Completion (Default: 0)

This bit indicates whether DMA transfer ended according to the current

DMA Channel Register setting.

1: DMA transfer ended normally.

0: DMA transfer has not ended since this bit was last cleared.

R/W1C

4 EXTDN

External DONE

Asserted

External Done Asserted (Default: 0)

This bit indicates whether an external I/O device asserted the DMADONE

*

signal. When the DMADONE

*

signal is set to bidirectional, this bit is also

set when the TX4937 asserts the DMADONE

*

signal.

1: DMADONE

*

signal was asserted.

0: DMADONE

*

signal was not asserted.

R/W1C

3 CFERR

Configuration

Error

Configuration Error (Default: 0)

Indicates whether an illegal register setting was made.

1: There was a configuration error.

0: There was no configuration error.

R/W1C

2

CHERR

Chain Bus Error

Chain Bus Error (Default: 0)

This bit indicates whether a bus error occurred while reading a DMA

Command Descriptor.

1: Bus error occurred.

0: No bus error occurred.

R/W1C

1

DESERR

Destination Error Destination Bus Error (Default: 0)

This bit indicates whether a bus error occurred during a destination bus

Write operation (a Write to a set DMDARn address).

1: Bus error occurred.

0: No bus error occurred.

R/W1C

0

SORERR

Source Bus Error Source Bus Error (Default: 0)

This bit indicates whether a bus error occurred during either a source bus

Read or Write operation (A Read or Write to a set DMSARn address).

1: Bus error occurred.

0: No bus error occurred.

R/W1C

Figure 8.4.3 DMA Channel Status Register (2/2)

Summary of Contents for TX49 TMPR4937

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Page 4: ......

Page 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Page 14: ...Table of Contents x ...

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4937 2005 3 Rev 2 0 ...

Page 44: ......

Page 52: ...Chapter 1 Overview and Features 1 6 ...

Page 156: ...Chapter 7 External Bus Controller 7 56 ...

Page 491: ...Chapter 16 Removed 16 1 16 Removed ...

Page 492: ...Chapter 16 Removed 16 2 ...

Page 493: ...Chapter 17 Removed 17 1 17 Removed ...

Page 494: ...Chapter 17 Removed 17 2 ...

Page 495: ...Chapter 18 Removed 18 1 18 Removed ...

Page 496: ...Chapter 18 Removed 18 2 ...

Page 497: ...Chapter 19 Removed 19 1 19 Removed ...

Page 498: ...Chapter 19 Removed 19 2 ...

Page 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

Page 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Page 542: ...Chapter 24 Parts Number when Ordering 24 2 ...