Chapter 8 DMA Controller

8-35

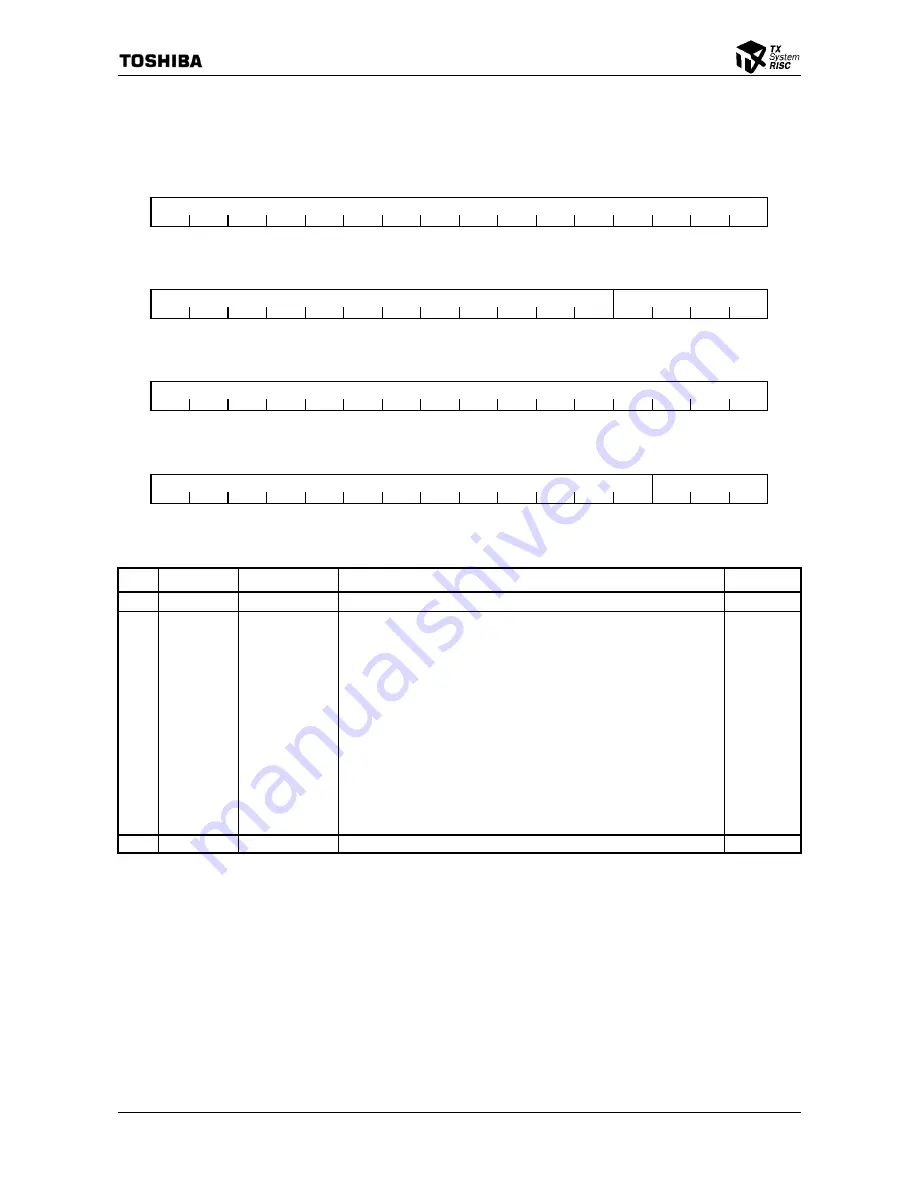

8.4.6

DMA Chain Address Register (DM0CHARn, DM1CHARn)

Offset Address: DMAC0 0xB000 (ch. 0) / 0xB040 (ch. 1) / 0xB080 (ch. 2) / 0xB0C0 (ch. 3)

DMAC1 0xB800 (ch. 0) / 0xB840 (ch. 1) / 0xB880 (ch. 2) / 0xB8C0 (ch. 3)

63

48

Reserved

: Type

: Initial value

47

36 35 32

Reserved CHADDR[35:32]

R/W

: Type

⎯

: Initial value

31

16

CHADDR[31:16]

R/W

: Type

⎯

: Initial value

15

3 2 0

CHADDR[15:3] Reserved

R/W R/W

: Type

⎯

: Initial value

Bit Mnemonic Field

Name

Description Read/Write

63:36 Reserved

⎯

35:3

CHADDR

Chain Address

Chain Address (Default: undefined)

When Chain DMA transfer is executed, this register sets the physical

address of the next DMA Command Descriptor to be read. If DMA transfer

according to the current Channel Register setting ends and the Chain

Enable bit (DMCCRn.CHNEN) is set, then the DMA Command Descriptor

is loaded in the Channel Register starting from the address indicated by

this register.

When a value other than “0” is set in this register, the Chain Enable bit

(DMCCRn.CHNEN) and the Transfer Active bit (DMCCRn.XFACT) are set.

When “0” is set in this register, only the Chain Enable bit

(DMCCRn.CHNEN) is cleared.

When the Chain Address field value reads a DMA Command Descriptor of

0, the value of this register is not updated and the value before that one

(address of the Data Command Descriptor when the value of the Chain

Address field being read was “0”) is held.

R/W

2:0 Reserved

R/W

Figure 8.4.6 DMA Chain Address Register

Summary of Contents for TX49 TMPR4937

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Page 4: ......

Page 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Page 14: ...Table of Contents x ...

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4937 2005 3 Rev 2 0 ...

Page 44: ......

Page 52: ...Chapter 1 Overview and Features 1 6 ...

Page 156: ...Chapter 7 External Bus Controller 7 56 ...

Page 491: ...Chapter 16 Removed 16 1 16 Removed ...

Page 492: ...Chapter 16 Removed 16 2 ...

Page 493: ...Chapter 17 Removed 17 1 17 Removed ...

Page 494: ...Chapter 17 Removed 17 2 ...

Page 495: ...Chapter 18 Removed 18 1 18 Removed ...

Page 496: ...Chapter 18 Removed 18 2 ...

Page 497: ...Chapter 19 Removed 19 1 19 Removed ...

Page 498: ...Chapter 19 Removed 19 2 ...

Page 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

Page 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Page 542: ...Chapter 24 Parts Number when Ordering 24 2 ...