3 General Safety Precautions and Usage Considerations

3-8

3.3.8 Thermal

design

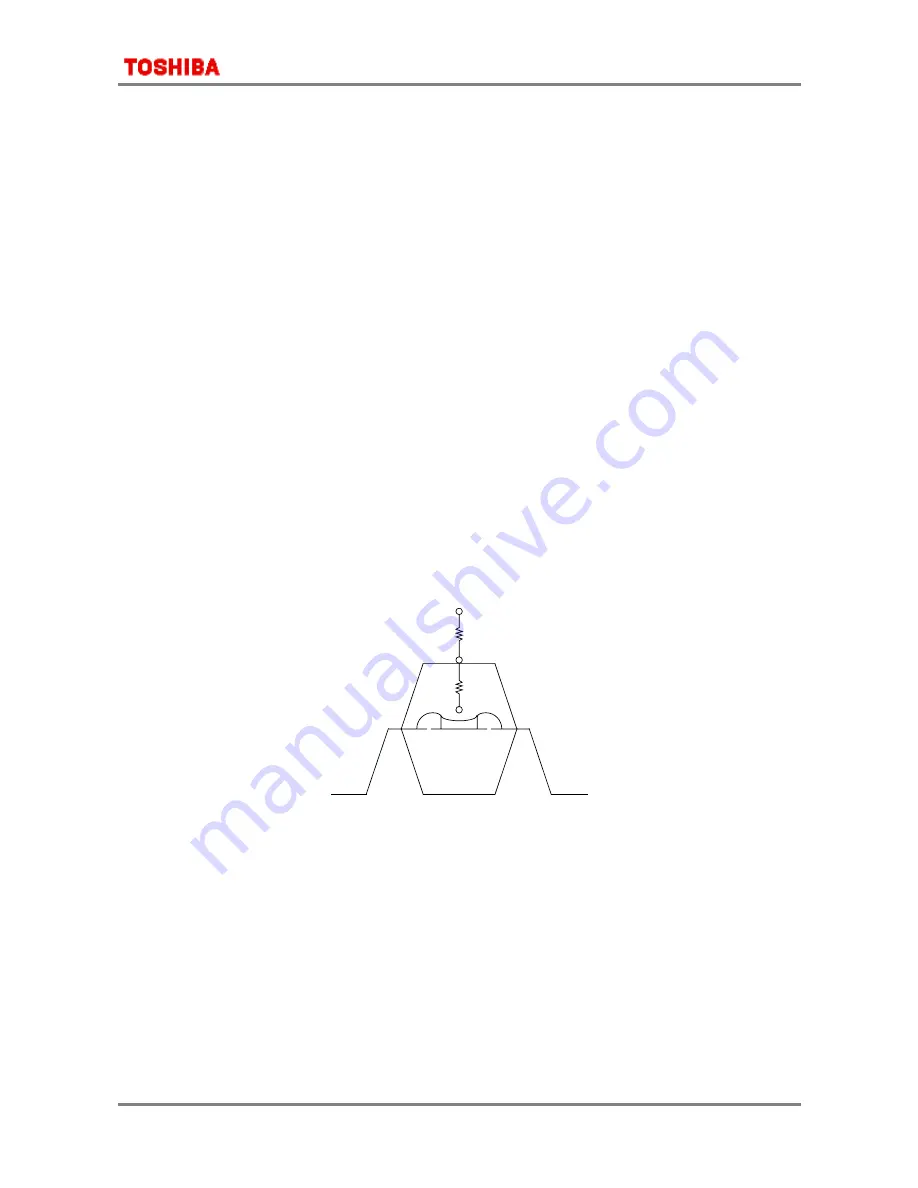

The failure rate of semiconductor devices is greatly increased as operating temperatures increase. As shown in

Figure 2, the internal thermal stress on a device is the sum of the ambient temperature and the temperature rise

due to power dissipation in the device. Therefore, to achieve optimum reliability, observe the following

precautions concerning thermal design:

(1) Keep the ambient temperature (Ta) as low as possible.

(2) If the device’s dynamic power dissipation is relatively large, select the most appropriate circuit board

material, and consider the use of heat sinks or of forced air cooling. Such measures will help lower the

thermal resistance of the package.

(3) Derate the device’s absolute maximum ratings to minimize thermal stress from power dissipation.

θ

ja =

θ

jc +

θ

ca

θ

ja = (Tj–Ta) / P

θ

jc = (Tj–Tc) / P

θ

ca = (Tc–Ta) / P

in which

θ

ja = thermal resistance between junction and surrounding air (°C/W)

θ

jc = thermal resistance between junction and package surface, or internal thermal

resistance

(°C/W)

θ

ca = thermal resistance between package surface and surrounding air, or external

thermal resistance (°C/W)

Tj = junction temperature or chip temperature (°C)

Tc = package surface temperature or case temperature (°C)

Ta = ambient temperature (°C)

P = power dissipation (W)

Tc

θ

ca

Ta

Tj

θ

jc

Figure 2 Thermal resistance of package

3.3.9 Interfacing

When connecting inputs and outputs between devices, make sure input voltage (V

IL

/V

IH

) and output voltage

(V

OL

/V

OH

) levels are matched. Otherwise, the devices may malfunction. When connecting devices operating at

different supply voltages, such as in a dual-power-supply system, be aware that erroneous power-on and power-

off sequences can result in device breakdown. For details of how to interface particular devices, consult the

relevant technical datasheets and databooks. If you have any questions or doubts about interfacing, contact your

nearest Toshiba office or distributor.

Summary of Contents for TX49 TMPR4937

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Page 4: ......

Page 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Page 14: ...Table of Contents x ...

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4937 2005 3 Rev 2 0 ...

Page 44: ......

Page 52: ...Chapter 1 Overview and Features 1 6 ...

Page 156: ...Chapter 7 External Bus Controller 7 56 ...

Page 491: ...Chapter 16 Removed 16 1 16 Removed ...

Page 492: ...Chapter 16 Removed 16 2 ...

Page 493: ...Chapter 17 Removed 17 1 17 Removed ...

Page 494: ...Chapter 17 Removed 17 2 ...

Page 495: ...Chapter 18 Removed 18 1 18 Removed ...

Page 496: ...Chapter 18 Removed 18 2 ...

Page 497: ...Chapter 19 Removed 19 1 19 Removed ...

Page 498: ...Chapter 19 Removed 19 2 ...

Page 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

Page 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Page 542: ...Chapter 24 Parts Number when Ordering 24 2 ...