Chapter 14 AC-link Controller

14-7

14.3.4 AC-link Start Up

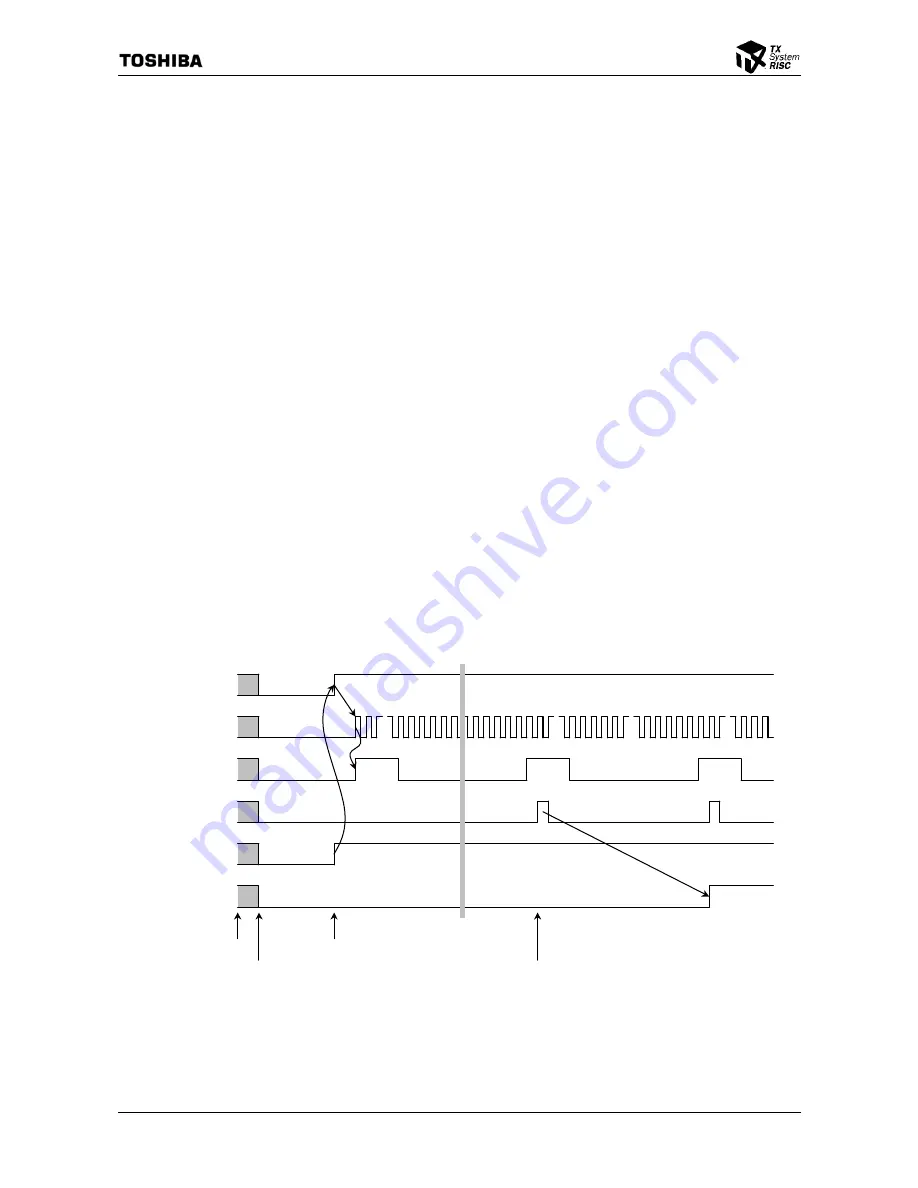

Figure 14.3.5 shows the conceptual sequence of AC-link start-up.

The ACLC Control Enable Register’s Enable AC-link bit is used to deassert/assert the

ACRESET

*

signal to the link side (including AC-link). This bit defaults to ‘0’, so the CPU asserts the

ACRESET

*

signal when it boots up.

The AC’97 specification requires that the reset assertion period is 1

µ

s or longer. The software is

responsible for controlling the length of this period.

The AC’97 specification also requires that the primary CODEC stops the AC-link clock (

BITCLK

)

signal during the period from

ACRESET

* signal assertion to 162.8ns after

ACRESET

* signal

deassertion. ACLC assumes the primary CODEC meet this requirement.

Deasserting the link-side reset makes the primary CODEC start driving the

BITCLK

signal. When

the

BITCLK

signal is provided, ACLC starts the

SYNC

signal output, which indicates the start of the

AC-link frame, and starts the frame-length counting.

When a CODEC becomes ready to receive access to its own register, the CODEC sets the “CODEC

Ready” bit of the Tag slot. When ACLC detects that this bit has been set, the ACLC Interrupt Status

Register (ACINTSTS)’s CODEC[1:0] Ready (CODEC[1:0]RDY) bit is set. The system software is

able to recognize the readiness of the CODEC(s) by detecting this event by way of either polling or

interrupt.

In case of 5.1 channel audio connection example (Figure 14.3.2), because the secondary CODEC is

connected to the

SDIN1

signal of ACLC, the software must watch ACINTSTS.CODEC1RDY bit to

determine the CODEC’s readiness for the register access.

Figure 14.3.5 Cold Reset and CODEC Ready Recognition

SDIN

ACRESET

*

BITCLK

SYNC

ENLINK

CODECRDY

ACLC internal clock becomes active

Software sets ENLINK bit

CODEC becomes ready to accept register access

Boot up

Note: The number of BITCLK cycles relative to other signals is not to scale.

Summary of Contents for TX49 TMPR4937

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Page 4: ......

Page 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Page 14: ...Table of Contents x ...

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4937 2005 3 Rev 2 0 ...

Page 44: ......

Page 52: ...Chapter 1 Overview and Features 1 6 ...

Page 156: ...Chapter 7 External Bus Controller 7 56 ...

Page 491: ...Chapter 16 Removed 16 1 16 Removed ...

Page 492: ...Chapter 16 Removed 16 2 ...

Page 493: ...Chapter 17 Removed 17 1 17 Removed ...

Page 494: ...Chapter 17 Removed 17 2 ...

Page 495: ...Chapter 18 Removed 18 1 18 Removed ...

Page 496: ...Chapter 18 Removed 18 2 ...

Page 497: ...Chapter 19 Removed 19 1 19 Removed ...

Page 498: ...Chapter 19 Removed 19 2 ...

Page 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

Page 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Page 542: ...Chapter 24 Parts Number when Ordering 24 2 ...