Chapter 21 Electrical Characteristics

21-12

Notes:

(1)

DMAREQ[n]

Edge Detection: Set the pulse width to 1.1

×

the GBUSCLK cycle or higher.

Level Detection: There is no AC characteristic definition. Continue asserting DMAREQ[3:0]

until DMAACK[3:0] is received.

(2)

DMAACK[n]

The DMAACK[n] signal is synchronous to SDCLK. (It is driven by GUBSCLK inside the chip.

See Chapter 6 for more information.)

The DMAACK[n] signal is asserted by SYSCLK or SDCLK for 3 cycles or more. However, this

is changed by the conditions [1] and [2] below.

[1] DMAC transfer mode (Single Address transfer, Dual Address transfer)

[2] Access time of the device DMAC accesses

•

When driving an external device with SYSCLK

Is asserted by SYSCLK for at least 3 cycles even in the shortest assertion case.

•

When driving an external device with SDCLK

Is asserted by SDCLK for at least 3 cycles even in the shortest assertion case. The AC

characteristics for Single Address transfer with SDRAM are tight, so we do not

recommend Single Address transfer.

(3)

DMADONE

*

Is asserted for only 1 SYSCLK cycle synchronous to SYSCLK.

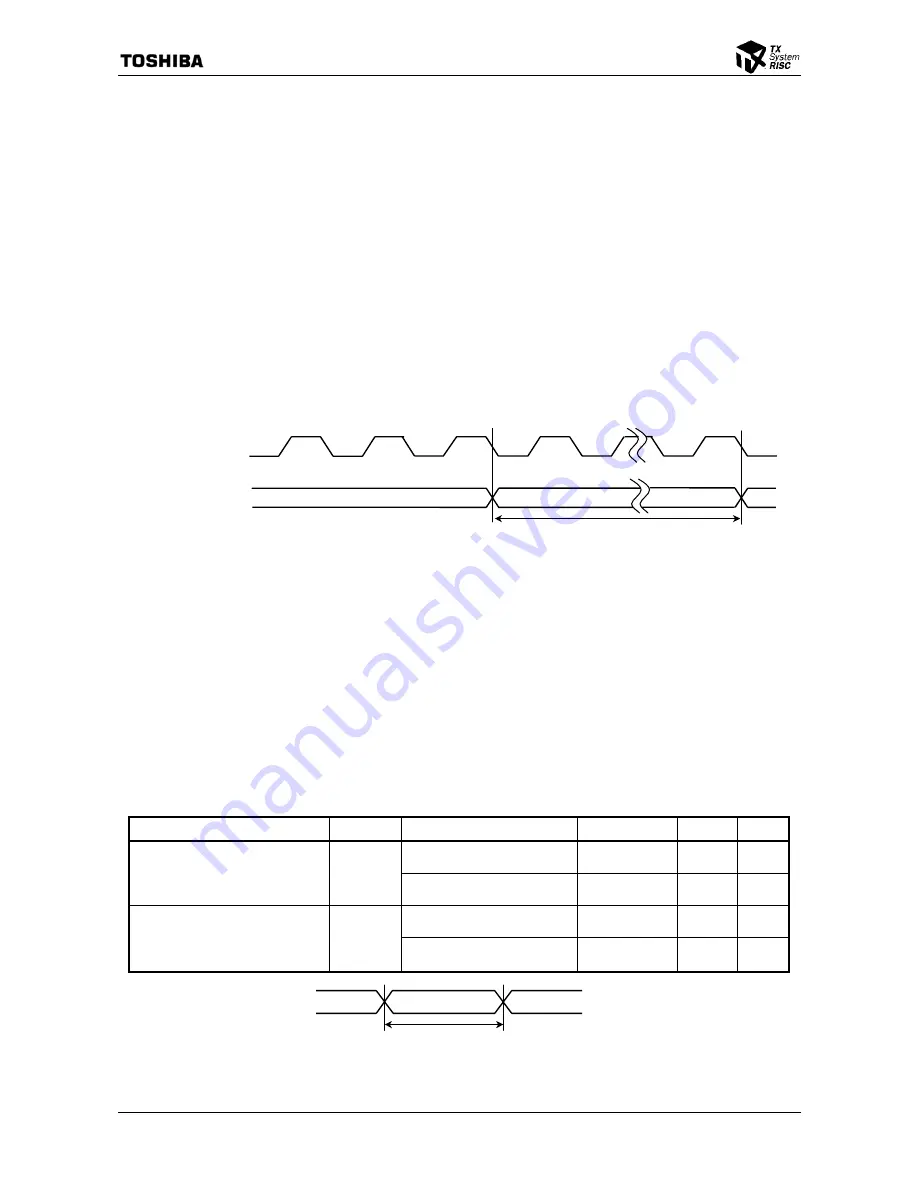

21.5.9 Interrupt Interface AC characteristics

(Tc

= 0 – 70

°

C, V

CCIO

= 3.3 V

±

0.2 V, V

CCInt

= 1.5 V

±

0.1 V, V

SS

= 0 V)

Item Symbol

Conditions Min.

Max.

Unit

Boot configuration

ADDR[2]=H

2

×

t

MCP

×

1.1

⎯

ns

INT Input Pulse Width Time

t

PW_INT

Boot configuration

ADDR[2]=L

1/2

×

t

MCP

×

1.1

⎯

ns

Boot configuration

ADDR[2]=H

t

MCP

×

1.1

⎯

ns

NMI Input Pulse Width Time

t

PW_NMI

Boot configuration

ADDR[2]=L

1/4

×

t

MCP

×

1.1

⎯

ns

Figure 21.5.10 Timing Diagram: INT/NMI Interface

t

PW_INT

/t

PW_NMI

Assertion Time

SDCLK[n]

DMAACK[n]

Summary of Contents for TX49 TMPR4937

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Page 4: ......

Page 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Page 14: ...Table of Contents x ...

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4937 2005 3 Rev 2 0 ...

Page 44: ......

Page 52: ...Chapter 1 Overview and Features 1 6 ...

Page 156: ...Chapter 7 External Bus Controller 7 56 ...

Page 491: ...Chapter 16 Removed 16 1 16 Removed ...

Page 492: ...Chapter 16 Removed 16 2 ...

Page 493: ...Chapter 17 Removed 17 1 17 Removed ...

Page 494: ...Chapter 17 Removed 17 2 ...

Page 495: ...Chapter 18 Removed 18 1 18 Removed ...

Page 496: ...Chapter 18 Removed 18 2 ...

Page 497: ...Chapter 19 Removed 19 1 19 Removed ...

Page 498: ...Chapter 19 Removed 19 2 ...

Page 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

Page 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Page 542: ...Chapter 24 Parts Number when Ordering 24 2 ...