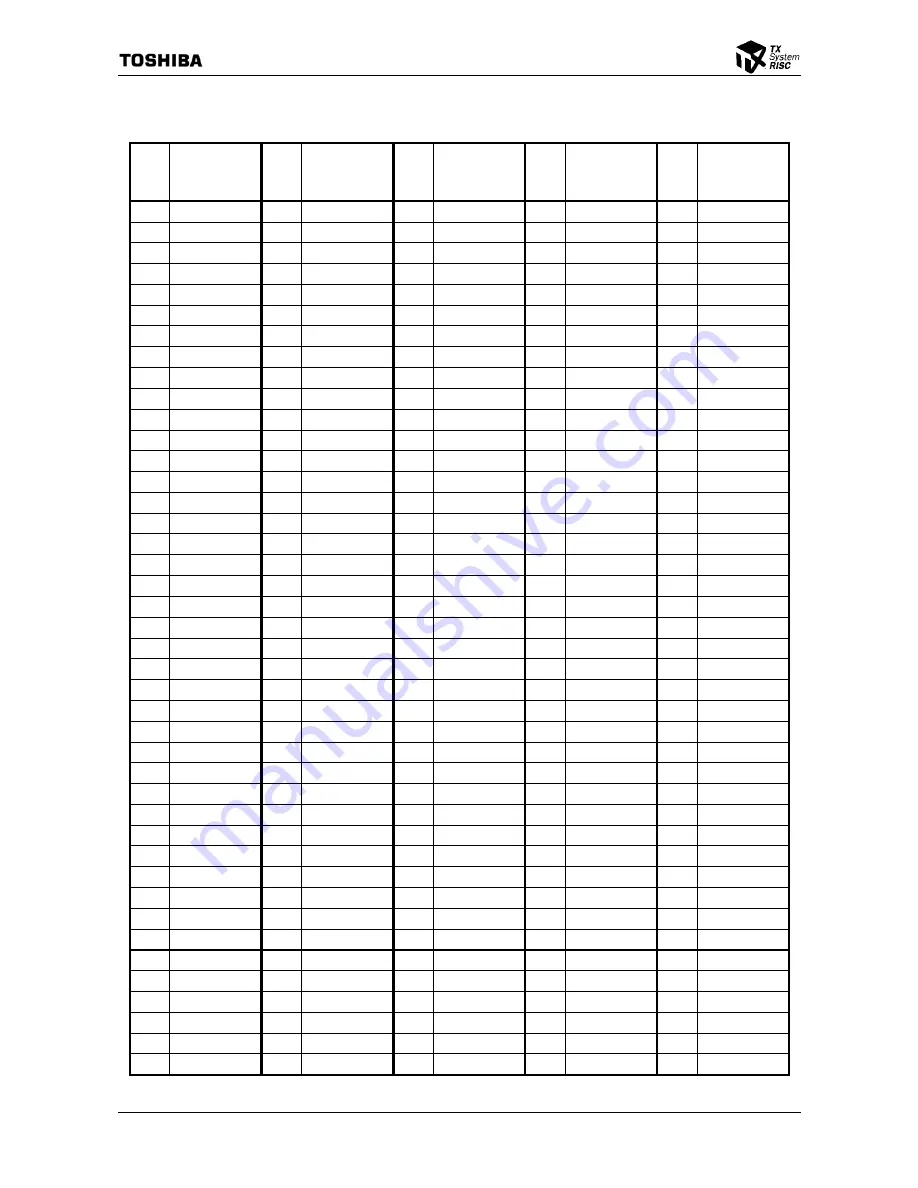

Chapter 22 Pinout and Package Information

22-4

Table 22.1.1 Pin Cross Reference by Pin Number (1/2)

Pin

Num-

ber

Pin Name

Pin

Num-

ber

Pin Name

Pin

Num-

ber

Pin Name

Pin

Num-

ber

Pin Name

Pin

Num-

ber

Pin Name

A1 PIO[1]

B17 PCIAD[0]

D7 CE[0]

*

E23

PCIAD[22]

J25

GNT[0]

*

A2 PIO[0]

B18 PCIAD[3]

D8 VddIN

E24 PCIAD[21]

J26 PCICLK[1]

A3 SWE

*

B19 PCIAD[6]

D9 VSS

E25 PCIAD[20]

K1 RESET

*

A4 CE[7]

*

B20 PCIAD[8]

D10 VddIN

E26 PCIAD[19]

K2 TEST[0]

*

A5 CE[5]

*

B21

PCIAD[12]

D11

DMAACK[0]

F1

INT[2] K3

HALTDOZE

A6 CE[4]

*

B22

C_BE[1]

D12

VddIO F2

INT[1] K4

VddIN

A7 DMAACK[2]

B23 PERR

*

D13

TPC[2] F3

INT[0] K5

VSS

A8 DMAACK[1]

B24 STOP

*

D14

VddIO F4

NMI

*

K22

VSS

A9 BWE[0]

*

B25

FRAME

*

D15

VddIN

F5

VddIN

K23

VddIN

A10 BWE[1]

*

B26

VSS

D16

VddIO

F22

VddIO K24

GNT[1]

*

A11 EEPROM_DI

C1 PIO[5]

D17 VddIN

F23 C_BE[3]

K25 REQ[0]

*

A12 EEPROM_DO C2 PIO[4]

D18 PCIAD[4]

F24 ID_SEL

K26 PCICLK[2]

A13 VSS

C3 VddIO

D19 VddIO

F25 VddIO

L1 SYSCLK

A14 EEPROM_SK C4 ACK

*

D20

M66EN

F26

PCIAD[23]

L2

TEST[4]

*

A15 EEPROM_CS C5 ACE

*

D21

VddIO G1

INT[5] L3

TEST[3]

*

A16 PCST[3]

C6 CE[2]

*

D22

SERR

*

G2

INT[4] L4

TEST[2]

*

A17 PCST[0]

C7 CE[1]

*

D23

VddIN G3

INT[3] L5

TEST[1]

*

A18 PCIAD[2]

C8 DMAREQ[3]

D24 TRDY

*

G4

RXD[0] L22

REQ[1]

*

A19 PCIAD[5]

C9 VddIO

D25 VddIO

G5 VddIN

L23 VSS

A20 C_BE[0]

C10 BWE[3]

*

D26

PCIAD[18]

G22

PCIAD[28]

L24

REQ[2]

*

A21 PCIAD[11]

C11 TDI

E1 TCLK

G23 PCIAD[27]

L25 GNT[2]

*

A22 PCIAD[15]

C12 TMS

E2 TIMER[0]

G24 PCIAD[26]

L26 PCICLK[3]

A23 VSS

C13 TPC[3]

E3 TIMER[1]

G25 PCIAD[25]

M1 OE

*

A24 VddIO

C14 PCST[7]

E4 VddIO

G26 PCIAD[24]

M2 WDRST

*

A25 IRDY

*

C15

PCST[4]

E5

VSS H1

TXD[0] M3

VddIO

A26 C_BE[2]

C16 PCST[1]

E6 SDIN[1]

H2 RTS[0]

*

M4

VddIN

B1 PIO[3]

C17 PCIAD[1]

E7 VddIO

H3 CTS[0]

*

M5

VSS

B2 PIO[2]

C18 VddIO

E8 VSS

H4 VddIO

M22 VSS

B3 BUSSPRT

*

C19

PCIAD[7]

E9

DMADONE

*

H5

VSS

M23

VddIO

B4 CE[6]

*

C20 PCIAD[9]

E10 VSS

H22 VSS

M24 REQ[3]

*

B5 VddIO

C21 PCIAD[13]

E11 DMAREQ[0]

H23 VddIN

M25 GNT[3]

*

B6 CE[3]

*

C22

PAR E12

VSS H24

PCIAD[29]

M26

PCICLK[4]

B7 DMAACK[3]

C23 LOCK

*

E13

TPC[1] H25

VddIO N1

DATA[1]

B8 DMAREQ[2]

C24 DEVSEL

*

E14

PCST[6] H26

PCICLK[0] N2

DATA[32]

B9 DMAREQ[1]

C25 PCIAD[17]

E15 VSS

J1 SCLK

N3 DATA[0]

B10 BWE[2]

*

C26

PCIAD[16]

E16

TRST

*

J2

TXD[1] N4

VSS

B11 TCK

D1 PIO[7]

E17 VSS

J3 RTS[1]

*

N5

VddIO

B12 DCLK

D2 VSS

E18 VSS

J4 CTS[1]

*

N22

PME

*

B13 TDO

D3 PIO[6]

E19 VSS

J5 RXD[1]

N23 VddIO

B14 PCST[8]

D4 VddIN

E20 PCIAD[10]

J22 PCIAD[31]

N24 VSS

B15 PCST[5]

D5 BYPASSPLL

*

E21

PCIAD[14]

J23

VSS

N25

DATA[63]

B16 PCST[2]

D6 VSS

E22 VSS

J24 PCIAD[30]

N26 PCICLK[5]

Summary of Contents for TX49 TMPR4937

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Page 4: ......

Page 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Page 14: ...Table of Contents x ...

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4937 2005 3 Rev 2 0 ...

Page 44: ......

Page 52: ...Chapter 1 Overview and Features 1 6 ...

Page 156: ...Chapter 7 External Bus Controller 7 56 ...

Page 491: ...Chapter 16 Removed 16 1 16 Removed ...

Page 492: ...Chapter 16 Removed 16 2 ...

Page 493: ...Chapter 17 Removed 17 1 17 Removed ...

Page 494: ...Chapter 17 Removed 17 2 ...

Page 495: ...Chapter 18 Removed 18 1 18 Removed ...

Page 496: ...Chapter 18 Removed 18 2 ...

Page 497: ...Chapter 19 Removed 19 1 19 Removed ...

Page 498: ...Chapter 19 Removed 19 2 ...

Page 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

Page 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Page 542: ...Chapter 24 Parts Number when Ordering 24 2 ...