Chapter 23 Notes on Use of TMPR4937

23-6

23.4 Note on PCI Controller

•

Set four target spaces, that are MEM0, MEM1, MEM2 and IO contained in PCI controller, so that

address windows are not duplicated. See 10.3.5 Target Access.

•

We recommend to set 0 to G2PTOCNT. See 10.4.14 G2P Timeout Count Register.

•

When TX4937 is the PCI target, access in dual address cycle is disabled. See 10.3.3 Supported PCI Bus

Commands.

•

Notes on Register Read by PCI Controller

Read the Power Status (PS) field in the PCISTATUS register (10.4.17) by the following procedures.

(1) Normal method

After checking that P2GSTATUS.PMCS bit is set, read the PCISTATUS.PS field.

(2) Method to read at any timing

To read the PCISTATUS.PS field directly without using the method (1), read the field twice

consecutively. The same value which is read twice consecutively is applied.

•

When writing to PCI bus by PDMAC of PCIC, don’t read on-chip SRAM or register in the controller

connected to G-Bus.

•

Restrictions on use of the broken master function in the PCI controller

[Restrictions]

When the broken master function in the PCI controller is used, the master which is not broken may

be incorrectly acknowledged to be broken.

•

Don’t use the broken master function

or

•

To use the broken master function, use only the high level containing Master A, B, C or D.

[Overview]

When the broken master function in the PCI controller is used, the master which is not broken may

be incorrectly acknowledged as the broken master.

The broken master detection function of the on-chip PCI bus arbiter detects the PCI master, which

does not start access though it has the bus, as the broken master and removes that PCI master from the

bus arbitration sequence.

When the broken master detection function detects the broken master, it may also detect the non-

broken master and acknowledge it as a broken master.

Summary of Contents for TX49 TMPR4937

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Page 4: ......

Page 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Page 14: ...Table of Contents x ...

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4937 2005 3 Rev 2 0 ...

Page 44: ......

Page 52: ...Chapter 1 Overview and Features 1 6 ...

Page 156: ...Chapter 7 External Bus Controller 7 56 ...

Page 491: ...Chapter 16 Removed 16 1 16 Removed ...

Page 492: ...Chapter 16 Removed 16 2 ...

Page 493: ...Chapter 17 Removed 17 1 17 Removed ...

Page 494: ...Chapter 17 Removed 17 2 ...

Page 495: ...Chapter 18 Removed 18 1 18 Removed ...

Page 496: ...Chapter 18 Removed 18 2 ...

Page 497: ...Chapter 19 Removed 19 1 19 Removed ...

Page 498: ...Chapter 19 Removed 19 2 ...

Page 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

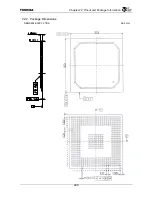

Page 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Page 542: ...Chapter 24 Parts Number when Ordering 24 2 ...