TMPR4937 Revision History

3

Page

Rev 1.1 Manual

Changes and Additions to Rev 1.1

5-13

Figure 5.2.6 G-Bus Arbiter Control Register

15 10 9 8

Reserved

⎯

ARBMD

R/W

R/W

1 1

7 6 5 0

Reserved

PRIORITY

R/W

00_01_10

15 14

Reserved

PRIORITY

R/W

000_001_010_011_100

0

PRIORITY

R/W

000_001_010_011_100

6-6

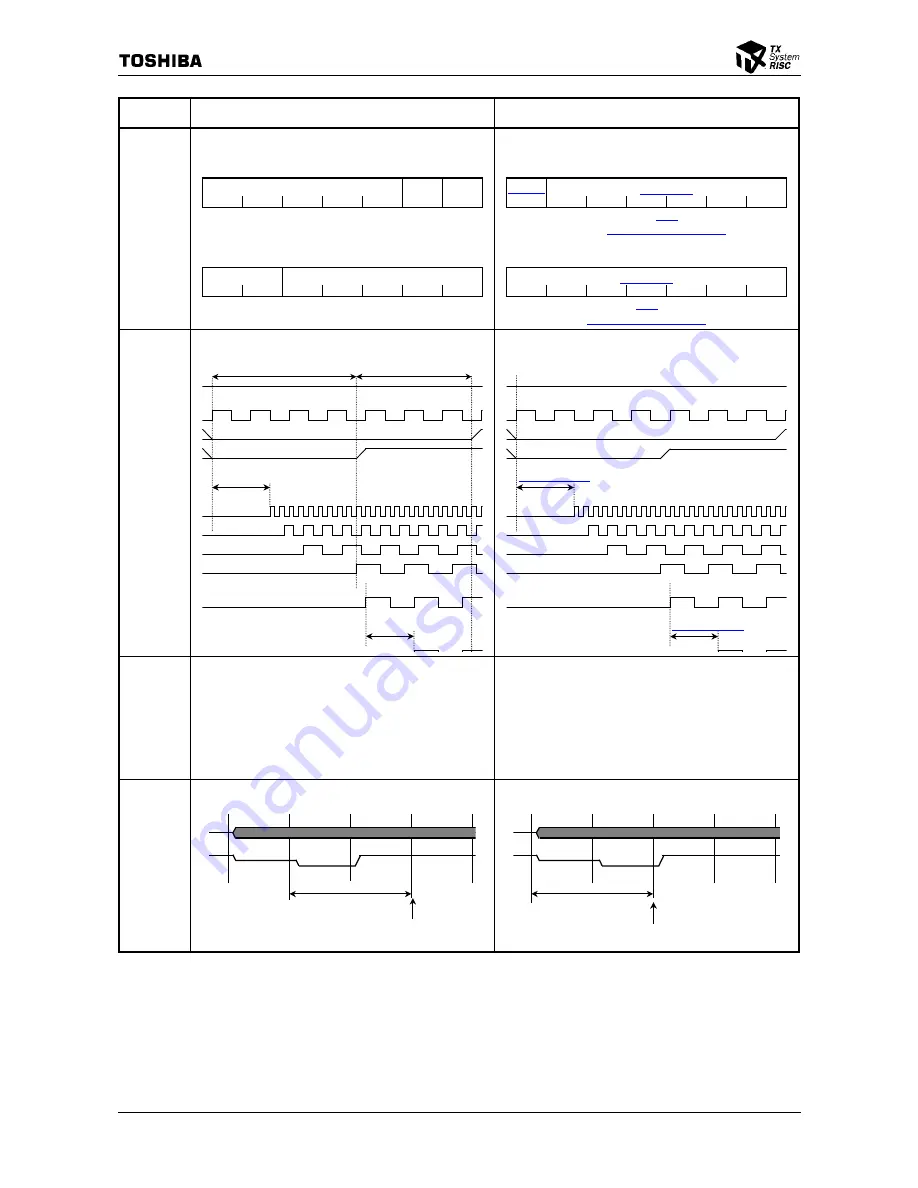

Figure 6.3.1 Power-On Sequence

ed back)

At least 100 ms (T.B.D)

PLL settling time (T.B.D)

(T.B.D)

PLL settling time (T.B.D)

ed back)

PLL settling time

PLL settling time

7-11

Added the following text to line 8 to Section 7.3.6.3,

Ready

Mode

When the number of wait cycles is 0, READY check is

started in 1 cycle after asserting the CE* signal. When the

number of wait cycles is other than zero, after waiting only

for the specified number of cycles, READY check is started.

7-11

Figure 7.3.3 Ready Mode

EBCCRn.PWT:WT=2

Start Ready Check

EBCCRn.PWT:WT=2

Start Ready Check

Summary of Contents for TX49 TMPR4937

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Page 4: ......

Page 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Page 14: ...Table of Contents x ...

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4937 2005 3 Rev 2 0 ...

Page 44: ......

Page 52: ...Chapter 1 Overview and Features 1 6 ...

Page 156: ...Chapter 7 External Bus Controller 7 56 ...

Page 491: ...Chapter 16 Removed 16 1 16 Removed ...

Page 492: ...Chapter 16 Removed 16 2 ...

Page 493: ...Chapter 17 Removed 17 1 17 Removed ...

Page 494: ...Chapter 17 Removed 17 2 ...

Page 495: ...Chapter 18 Removed 18 1 18 Removed ...

Page 496: ...Chapter 18 Removed 18 2 ...

Page 497: ...Chapter 19 Removed 19 1 19 Removed ...

Page 498: ...Chapter 19 Removed 19 2 ...

Page 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

Page 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Page 542: ...Chapter 24 Parts Number when Ordering 24 2 ...