Chapter 6 Clocks

6-1

6. Clocks

6.1 TX4937

Clock

Signals

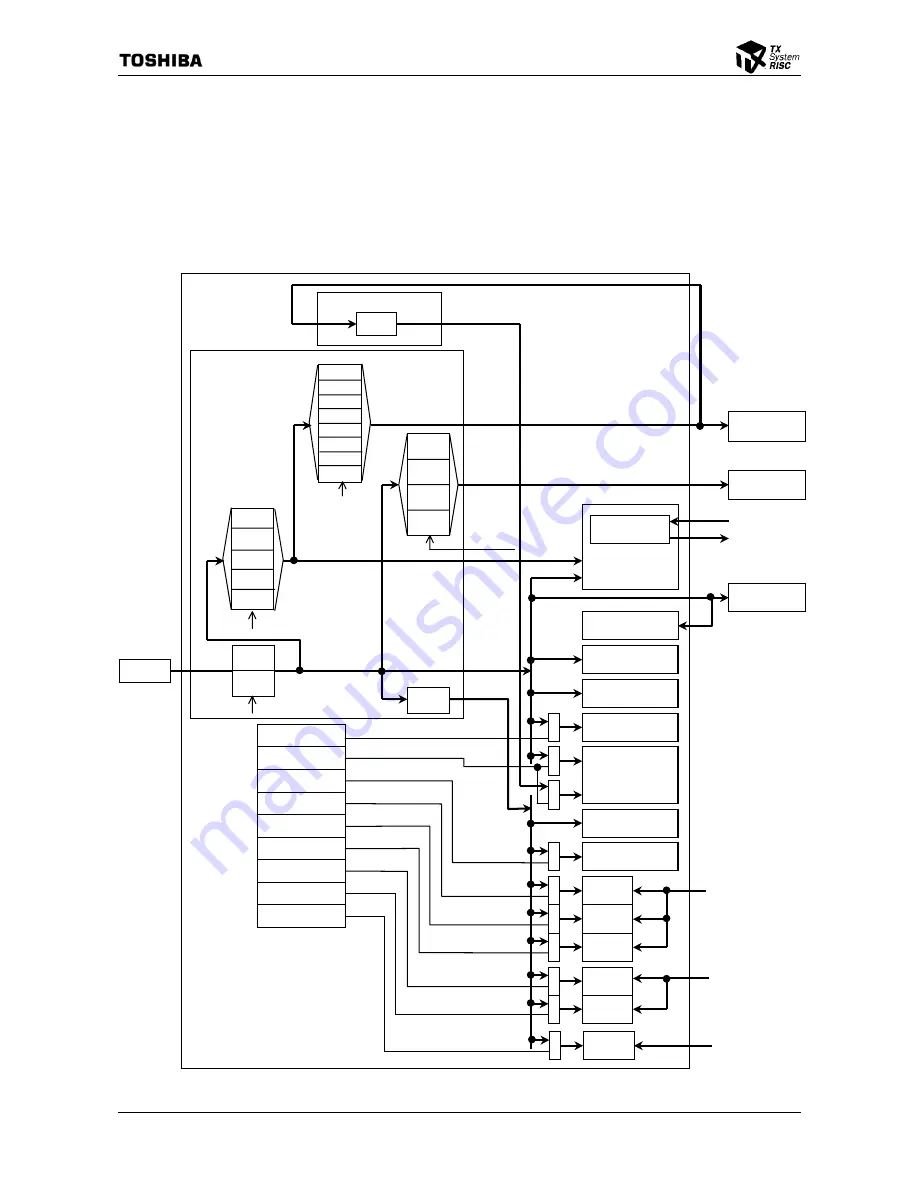

Figure 6.1.1 shows the configuration of TX4937 blocks and clock signals. Table 6.1.1 describes each clock

signal. Table 6.1.2 shows the relationship among different clock signals when the CPU clock frequency is

266 MHz. Table 6.1.3 shows the relationship among different clock signals when the CPU clock frequency is

300 MHz. Table 6.1.4 shows the relationship among different clock signals when the CPU clock frequency is

333 MHz.

Figure 6.1.1 TX4937 Block and Clock Configuration

SDRAMC

PCIC

TX49/H3 core

IRC

EBUSC

DMAC

CPUCLK

GBUSCLK

IMBUSCLK

CLKCTR

MASTERCLK

CG

SYSCLK

SDCLK[3:0]

SDCLKIN

PCICLK[5:0]

PCICLKIN

TX4937

Data input latch

CLKGATE

PCICLKO

×

1

TCLK

1/2

ADDR[3][1:0]

PLL1

ADDR[11:10]

(CCFG.

PCIDIVMODE)

ADDR[14:13]

PCI device

External

device

PLL2

Oscillator

×

1

1/1

1/2

1/3

1/4

DMACKD

PCICKD

PIOCKD

TM2CKD

TM1CKD

TM0CKD

SIO1CKD

PIO

CLKGATE

TMR2

TMR1

TMR0

SIO1

SIO0

SIO0CKD

SDRAM

SCLK

ACLCKD

ACLC

BITCLK

×

4

EJTAG/DSU

DCLK

TCK

ADDR[2]

1/4

1/4.5

1/5

1/5.5

1/8

1/9

1/10

1/11

×

2

×

2.5

×

3

×

4

x4.5

Summary of Contents for TX49 TMPR4937

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Page 4: ......

Page 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Page 14: ...Table of Contents x ...

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4937 2005 3 Rev 2 0 ...

Page 44: ......

Page 52: ...Chapter 1 Overview and Features 1 6 ...

Page 156: ...Chapter 7 External Bus Controller 7 56 ...

Page 491: ...Chapter 16 Removed 16 1 16 Removed ...

Page 492: ...Chapter 16 Removed 16 2 ...

Page 493: ...Chapter 17 Removed 17 1 17 Removed ...

Page 494: ...Chapter 17 Removed 17 2 ...

Page 495: ...Chapter 18 Removed 18 1 18 Removed ...

Page 496: ...Chapter 18 Removed 18 2 ...

Page 497: ...Chapter 19 Removed 19 1 19 Removed ...

Page 498: ...Chapter 19 Removed 19 2 ...

Page 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

Page 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Page 542: ...Chapter 24 Parts Number when Ordering 24 2 ...