A

B

C

D

E

F

G

H

A

B

C

D

E

F

G

H

2

1

3

4

5

6

7

8

2

1

3

4

5

6

7

8

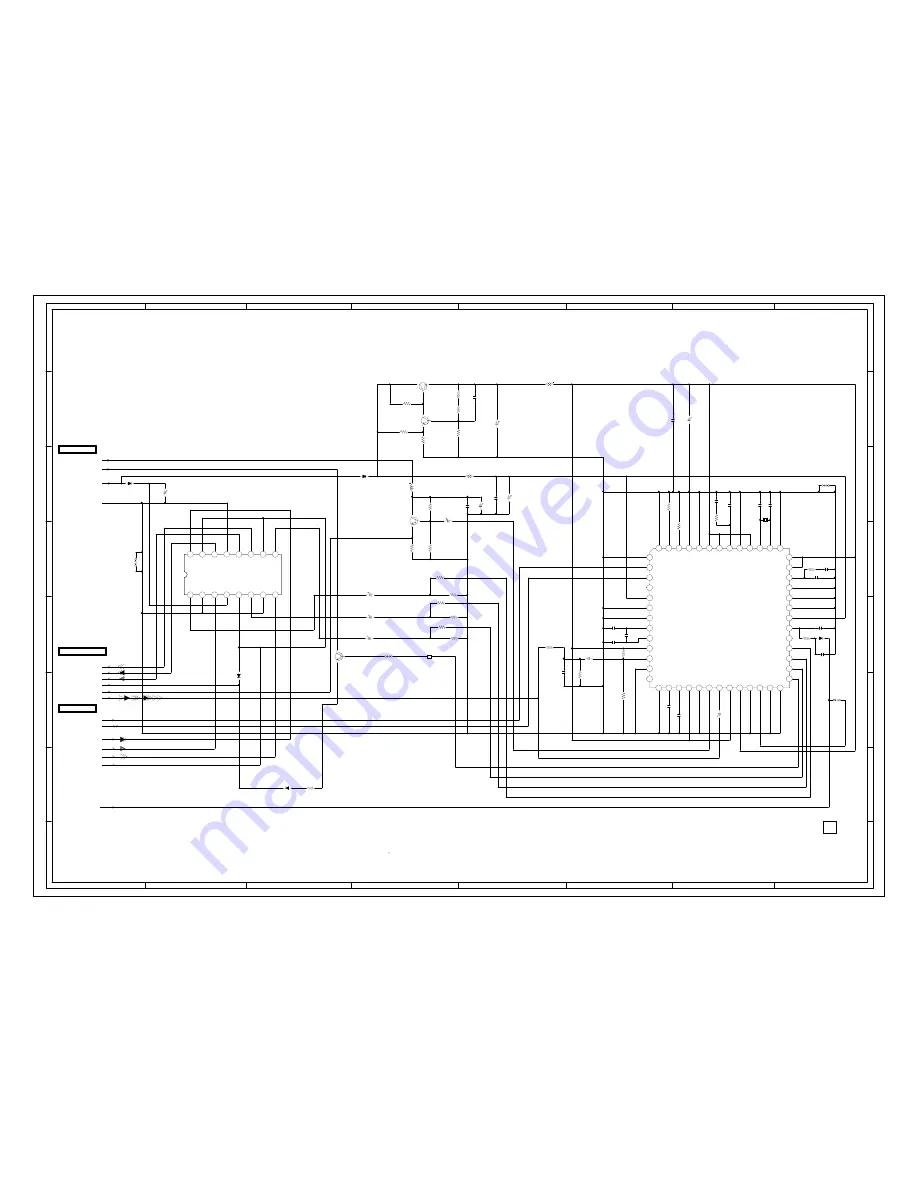

IC1202

MM1231XF

TRIPLE ANALOG MPXER IC

1

10

11

12

13

14

15

16

2

3

4

5

6

7

8

9

IC1201

ET-TVT008B

T’TEXT IC

1

10

11

12

13

14

15

16

17

18

19

2

20

21

22

23

24

25

26

27

28

29

3

30

31

32

33

34

35

36

37

38

39

4

40

41

42

43

44

45

46

47

48

49

5

50

51

52

6

7

8

9

B1201

W4BRH3.5X6X1.0

C1207

47

16V

KANP

D1203

SB140-EIC

D1202

11E1-EIC

D1252

1SS133

D1261

1SS133

D1201

AK04

OF PRINTING AND SUBJECT TO CHANGE WITHOUT NOTICE

NOTE: THIS SCHEMATIC DIAGRAM IS THE LATEST AT THE TIME

X1201

100CT01302

13875KHz

L1205

10uH

C1284

100

6.3V

YK

C1205

47

16V

YK

C1206

47

16V

YK

C1214

47

16V

KA

C1103

220

6.3V

KA

C1215

0.022

B

C1218

1 B

C1204

0.01

B

C1213

0.1

B

C1259

33P

CH

C1220

0.1 B

C1212

0.1

F

C1211

0.1

B

C1255

0.1

F

C1216

0.1

B

C1209

0.1

B

C1208

0.1

B

C1210

0.47

B

C1219

0.022 B

C1217

33P

CH

C1201

56P

CH

C1102

680P

CH

C1203

0.47

TF

R1204

150

R1262

390

1/4W

R1203

1K

R1202

1K

R1251

100

R1206

100

R1272

10K

R1207

10K

R1212

1.5K

R1214

1.5K

R1213

1.5K

R1256

100

R1280

100

R1254

47K

R1253

22K

R1255

120

R1117

68

R1115

560

R1108

820

R1211

560

R1209

470

R1118

1.8K

R1119

120

R1120

1K

R1289

3.3K

1/4W

C1274

100

16V

YK

C1202

100

16V

YK

C1273

100

16V

YK

C1257

100

6.3V

KA

C1256

100

6.3V

YK

Q1253

2SC2412K

SYNC BUFFER

Q1262

2SC2412K

BLK BUFFER

Q1101

KTD863_Y

REG

Q1104

2SC2412K

BUFFER

W884

W876

W838

W867

L1204

100uH

0305

L1203

10uH 0305

DURING PLAYBACK.

MEASURED WITH THE DIGITAL TESTER

NOTE:THE DC VOLTAGE EACH PART WAS

P.CON+9V

P.CON+5V_C

AT+5.6V

GND

TEXT_B

TEXT_R

TEXT_G

TEXT_Y

TEXT_SYNC

SW_VIDEO

SCL

SDA

OSD_R

OSD_G

OSD_B

OSD_Y

TEXT_RESET

PCB010

VMC295

NC

IN3A

IN3B

1.7

4.8

0

0.3

NC

NC

CS1

SCL

SDA

TDO

VDD5V1

GNDA1A

VREFP

VREFN

VDDA1

VINP

GNDA1B

GNDA2

VBG

VCM

VDDA2

GNDA3

SYNC

GND5V2

STANDBY

TSTIO

SCEN

GREEN

RED

MUTE

RSTB

VDD5V2

GND3V5

GND3V1A

PLLRC1

VDD3V1B

VDD3V1A

VDD3V2

52 CS0

51 FLAG2

FLAG1

TSTAPP

GND5V1

VDD3V4

VDD3V3

PLLRC2

GND3V3

42 OSC OUT

40 GND2V3

41 OSC IN

27 BLANK

28 BLUE

GND3V1B

VDD3V5

VDDA3

VIDEO IN

GND3V4

4.8

IN1B

SW1

OUT1

GND2

OUT2

OUT3

SW3

IN2A

SW2

VCC

IN2B

GND1

IN1A

GND3

0

1.5

0

5.0

5.0

5.0

0

0

2.2

1.1

3.3

1.6

0

0

1.3

1.6

3.3

0

2.9

2.9

3.3

3.3

0

0

0

5.0

0

0

0

5.0

5.0

0

0

0

1.4

3.3

3.3

0

1.3

1.3

3.3

0

1.4

3.3

3.3

0

0

0

0

0

2.3

5.0

3.3

3.8

3.8

0.9

0.4

FROM REGULATOR

T’TEXT SCHEMATIC DIAGRAM

(SYSCON PCB)

1.6

0

0.8

0

0.8

0.8

0

1.5

0

1.6

5.1

1.5

1.6

0

FROM/TO CHROMA/IF

FROM/TO MICON