User's Manual l MBa8MPxL UM 0100 l © 2022, TQ-Systems GmbH

Page 5

2.2

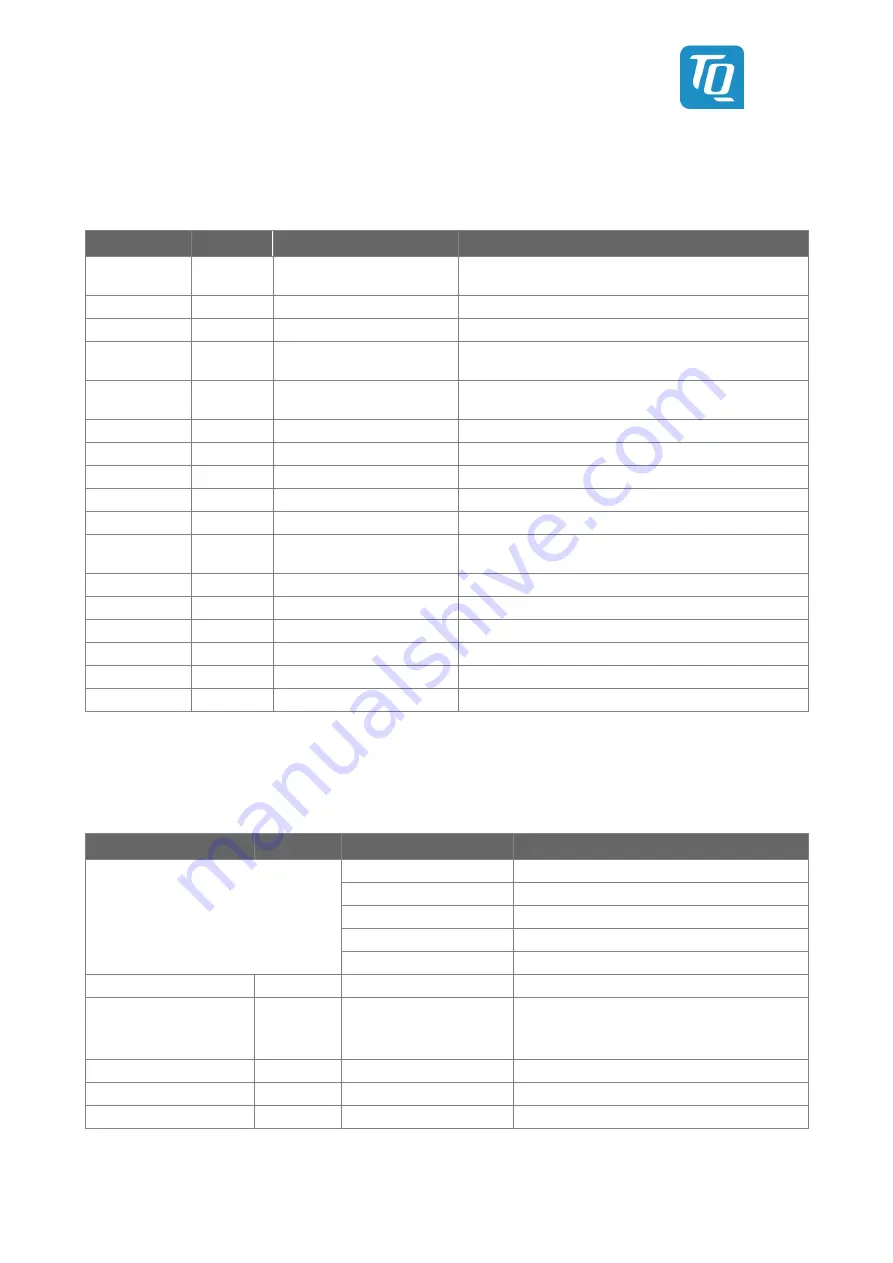

MBa8MPxL interfaces, overview

The following interfaces/functions and user interfaces are available on the MBa8MPxL:

Table 2:

Data interfaces

Interface

Connector

Type

Remark

Audio

X15, X16,

X17

3 × 3.5 mm jack

MIC (mono), Line-in (stereo), Line-out (stereo)

CAN FD

X18, X19

MC 1,5/ 3-G-3,5

X18: CAN0 | X19: CAN1

eDP / DP

X65

DisplayPort

DSI-to-DP bridge

Eth 1000 Base-T

X66

Double RJ45

Gigabit PHY DP83867 and socket with integrated

transformers

GPIO / ADC

X555

DMC 1,5/15-G1F-3,5-LR

P20THR

Connected to IO bank, usage up to 24 V (GPIO)

HDMI

X44

HDMI

–

I

2

C

X61

40-pin, 50 mil pin header

4 × I

2

C

JTAG

X22

10-pin, 50 mil pin header

JTAG

LVDS CMD

X7

20-pin, DF19G

ZIF con USB 2.0

LVDS Data

X11

30-pin, DF19G

ZIF connector

MIPI CSI

X57

60-pin, 0.8 mm, TE

Connectivity

CSI1 and CSI2

PCIe / M.2

X48

M.2

PCIe + USB 2.0

SIM card

X46

SIM card holder

SIM card slot

SD card

X42

USDHC2

Optional boot source and supply of module

USB 3.0

X36

Stacked Type A

USB 3.0 H1, top, USB 3.0 H2, bot

USB 3.0 OTG

X29

USB1-Interface at USB Micro-B USB OTG or Serial Download Mode

USB Debug

X28

UART3, UART4

Via FTDI chip to micro USB AB socket

The MBa8MPxL provides the following diagnostic and user interfaces:

Table 3:

Diagnostic and user interfaces

Interface

Reference

Component

Remark

Status LEDs

1 × Red LED

Reset

7 × Green LED

Voltages on MBa8MPxL

2 × Green LED

General purpose LEDs

3 × Orange LED

V_3V3_MOD, V_3V3_SD, V_1V8_MOD

1 × Yellow LED

General purpose LED

Temperature sensor

D1

1 × SE97BTP

Digital I

2

C temperature sensor

Power / Reset

S7

S8

S9

3 × Pushbutton

Reset

PMIC reset

CPU-ON/OFF

GP button

S12, S13

2 × Pushbutton

General purpose pushbuttons

Boot-Mode

S1

1 × 4-fold DIP switch

Boot Device selection

Coin cell

X56

1 × battery socket

Standard CR2032, RTC buffer