User's Manual l MBa8Xx UM 0100 l © 2020, TQ-Systems GmbH

Page 4

2.

BRIEF DESCRIPTION

This User's Manual describes the hardware of the MBa8Xx as of revision 02xx. The MBa8Xx is designed as a carrier board for the

TQ-Minimodules TQMa8Xx and TQMa8Xx4. If not described differently, all descriptions apply to both TQMa8Xx and TQMa8Xx4.

For better readability, the TQMa8Xx is therefore named for both, the TQMa8Xx and the TQMa8Xx4.

Core of the MBa8Xx is the TQMa8Xx with an NXP i.MX 8X CPU.

The TQMa8Xx connects all peripheral components. In addition to the standard communication interfaces such as USB, Ethernet,

etc., all other available signals of the TQMa8Xx are routed on 100 mil standard pin headers on the MBa8Xx.

CPU features and interfaces can be evaluated, software development for a TQMa8Xx based project can start immediately.

Currently three i.MX 8X derivatives are supported:

1.

i.MX 8DualX (Dual Cortex

®

-A35)

2.

i.MX 8DualXPlus (Dual Cortex

®

-A35)

3.

i.MX 8QuadXPlus (Quad Cortex

®

-A35)

Note: i.MX 8DualX, reduced functionality

The information in this document primarily refers to the i.MX 8DualXPlus and i.MX 8QuadXPlus.

The i.MX 8DualX is not considered in this document because some interfaces are not available or have

limitations. Details can be found in the TQMa8Xx User’s Manual.

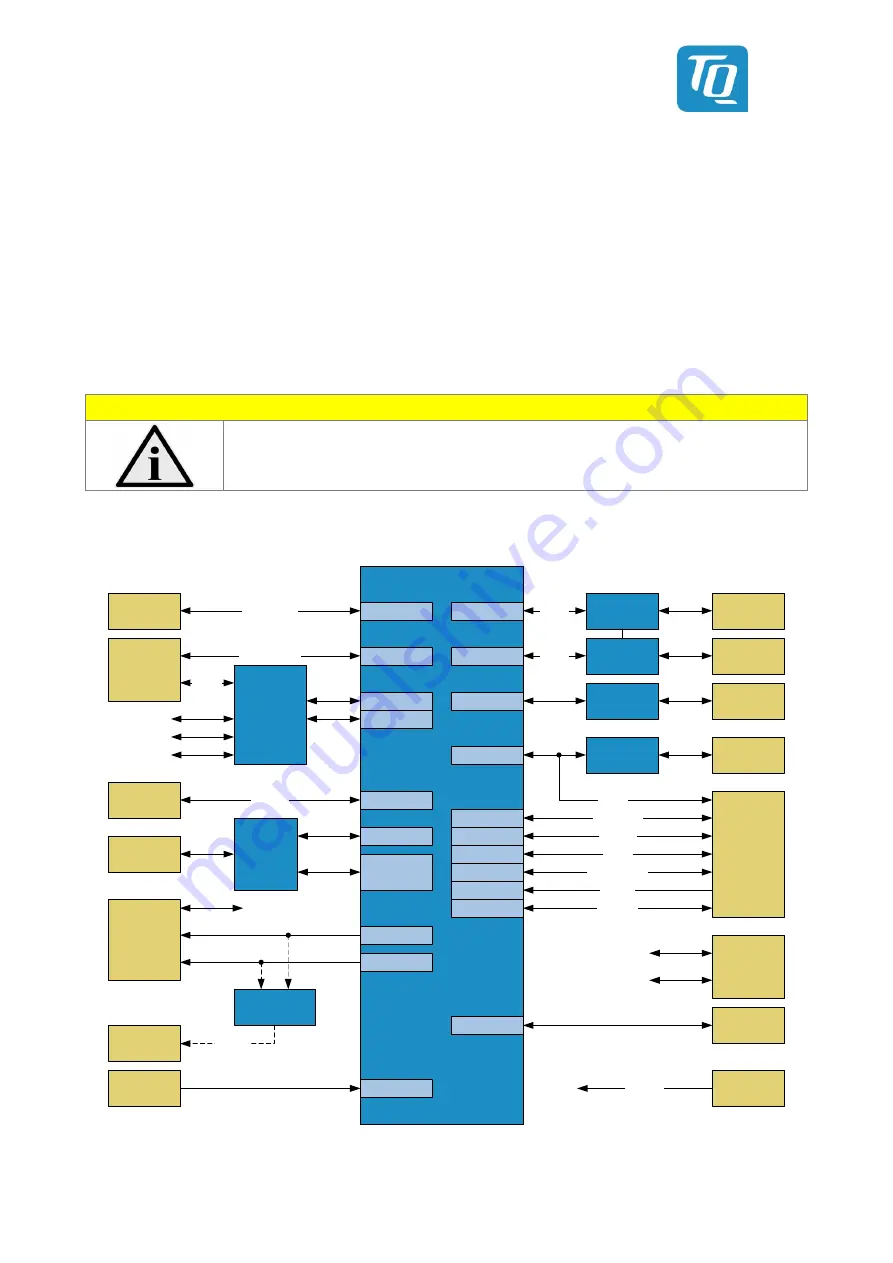

2.1

MBa8Xx block diagram

TQMa8Xx

Ethernet

1G

PHY

DP83867

RGMII

ENET0

RGMII

SD card

uSDHCx

SD SDR104

UART

USB

Debug

JTAG

ENET1

FT4232

JTAG

PHY

DP83867

Ethernet

1G

Headers

QSPI1

1x QSPI

CAN0/1

2x 3-pin

Header

2x CAN-FD

Transceiver

SPI

3x SPI

Mini PCIe

Slot

PCIe

PCIe-Lane x1

OTG2

OTG1

USB OTG

2.0

USB 2.0

TAMPER

10x TAMPER

ADC

4x ADC

LVDS

LVDS0/DSI0

Audio In/

Out

SAI

Codec

LVDS1/DSI1

USB Hub

TUSB8041

Host 1

Host 2

Host 3

Host 4

Host 2

USB 3.0

Typ A (2x)

Host 3

Host 4

Display

Port

optional

SN65DSI

USB SS

SCU

UART

MIPI CSI

CSI

Power-In

24 V DC

I2C

2x (4x) I2C

1x SAI

1x UART

UART1

Figure 1:

Block diagram MBa8Xx