S

S

S

D

D

D

8

8

8

0

0

0

s

s

s

e

e

e

r

r

r

i

i

i

e

e

e

s

s

s

Rev1.2

SD80 Secure Digital Card

Transcend Information Inc.

14

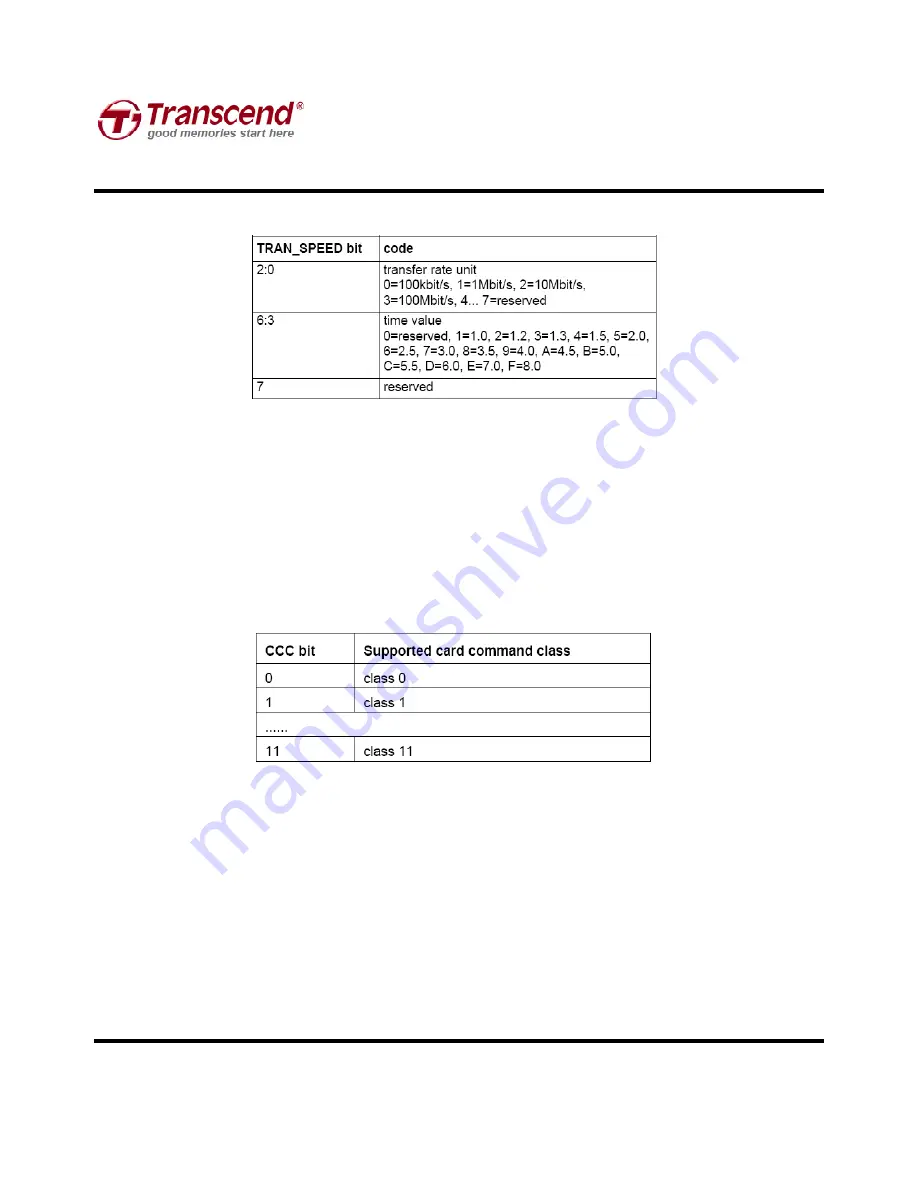

Note that for current SD Memory Cards that field must be always 0_0110_010b (032h) which is equal to 25MHz - the

mandatory maximum operating frequency of SD Memory Card.

In High-Speed mode, that field must be always 0_1011_010b (05Ah) which is equal to 50MHz. And when the timing

mode returns to the default by CMD6 or CMD0 command, its value will be 032h.

•

CCC

The SD Memory Card command set is divided into subsets (command classes). The card command class register

CCC defines which command classes are supported by this card. A value of ‘1’ in a CCC bit means that the

corresponding command class is supported.

•

READ_BL_LEN

This field is fixed to 9h, which indicates READ_BL_LEN=512 Byte.

•

READ_BL_PARTIAL

This field is fixed to 0, which indicates partial block read is inhibited and only unit of block access is allowed.

•

WRITE_BLK_MISALIGN

This field is fixed to 0, which indicates write access crossing physical block boundaries is always disabled in High

Capacity SD Memory Card.

•

READ_BLK_MISALIGN