TE0600 TRM

Revision: V3.02

Copyright © 2017 Trenz Electronic GmbH

Page of

2

33

http://www.trenz-electronic.de

Table of Contents

Overview _____________________________________________________________________________ 4

Block diagram _______________________________________________________________________ 4

Main components ____________________________________________________________________ 4

Key features ________________________________________________________________________ 5

Initial Delivery State ___________________________________________________________________ 5

Power Consumption __________________________________________________________________ 6

Detailed Description ____________________________________________________________________ 7

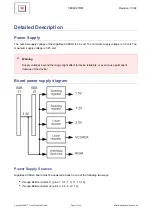

Power Supply _______________________________________________________________________ 7

Board power supply diagram ____________________________________________________________ 7

Power Supply Sources _____________________________________________________________ 7

FPGA banks VCCIO power supply ____________________________________________________ 8

On-board Power Rails ______________________________________________________________ 8

Power Supervision ___________________________________________________________________ 10

Power-on Reset __________________________________________________________________ 10

Power Fail ______________________________________________________________________ 11

Board-to-board Connectors ____________________________________________________________ 11

Connector Mechanical Ratings ______________________________________________________ 12

Manufacturer Documentation _______________________________________________________ 12

EPROM ___________________________________________________________________________ 12

DDR3 SDRAM Memory _______________________________________________________________ 12

Flash Memory ______________________________________________________________________ 13

Ethernet ___________________________________________________________________________ 13

Oscillators _________________________________________________________________________ 14

User LED __________________________________________________________________________ 15

Watchdog _________________________________________________________________________ 15

Configuration Options __________________________________________________________________ 17

JTAG Configuration __________________________________________________________________ 17

Flash Configuration __________________________________________________________________ 17

eFUSE Programming ________________________________________________________________ 17

B2B Connectors Pin Descriptions ________________________________________________________ 18

Pin Labeling ________________________________________________________________________ 18

Pin Numbering ______________________________________________________________________ 18

Pin Types __________________________________________________________________________ 19

External Bank 2 differential clock connection ______________________________________________ 20

J1 Pin-out _________________________________________________________________________ 20

J2 Pin-out _________________________________________________________________________ 22

Signal Integrity Considerations _________________________________________________________ 24

Module revisions and assembly variants ___________________________________________________ 25

Related Materials and References ________________________________________________________ 27

Data Sheets ________________________________________________________________________ 27

Documentation Archives ______________________________________________________________ 27

User Guides ________________________________________________________________________ 27