TE0600 TRM

Revision: V3.02

Copyright © 2017 Trenz Electronic GmbH

Page

of

14

33

http://www.trenz-electronic.de

1.

2.

3.

4.

5.

Caution

For correct operation of the Marvell PHY it is required that PHY Reset pin sees valid low level

each time power is applied and also during any brownout situations where system Power is

removed for short time, but some pins are not at valid logic levels.

Solutions:

if GbE PHY is not used PHY reset pin can be tied off to GND

if PLL is used from PHY clock, then PLL "locked" output can be used to reset PHY - as long

PLL is not locked, it will keep PHY in reset

Reset pulse generation circuit clocked from FPGA internal configuration clock, this circuit

can force PHY reset pin to low when external clock from PHY is not available

any custom Reset circuit that is guaranteed to drive PHY reset to low level at least once

after FPGA configuration when PHY clock is not running.

any user logic that is guaranteed to drive PHY reset low after FPGA configuration (without

using PHY clock).

Explanation: Marvell PHY samples the MODE pins ONLY when it sees low level on PHY reset

input, it does not sample those pins during short power off situations (if the reset pin holds high

level because of pin capacitance and high impedance of the pins)! So it is possible that the PHY

mode is reset, but the mode pins are not sampled again - this yields in mode setting where

125MHz reference clock from PHY is not available.

Oscillators

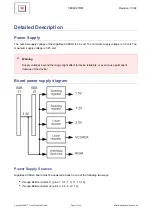

The module has one 25 MHz oscillator for Ethernet PHY (U9). Ethernet PHY provides clock multiplication

and resulting 125 MHz clock acts as a system and user clock for the FPGA (FPGA input pin AA12).

Caution

Note: For correct generation start, PHY should receive reset pulse. Recommended way to do it it's

to connect PHY reset signal (ETHERNET_PHY_RST_N) to LOCKED output of corresponding

DCM (DCM which use 125 MHz from PHY).

The module also provides the footprint for custom 3.3 V single-ended oscillator (U12) which can be installed

as an option (FPGA input pin Y13).