TE0600 TRM

Revision: V3.02

Copyright © 2017 Trenz Electronic GmbH

Page

of

20

33

http://www.trenz-electronic.de

External Bank 2 differential clock connection

TE0600-02 module have optional connection to FPGA bank 2 differential clock input pins. To provide

connection from B2B_B2_L41_P signal to Y13 FPGA pin, zero-resistor R69 should be soldered. To provide

connection B2B_B2_L41_N signal to AB13 FPGA pin, zero-resistor R81 should be soldered. Note that in

this case optional user oscillator U13 can't be used.

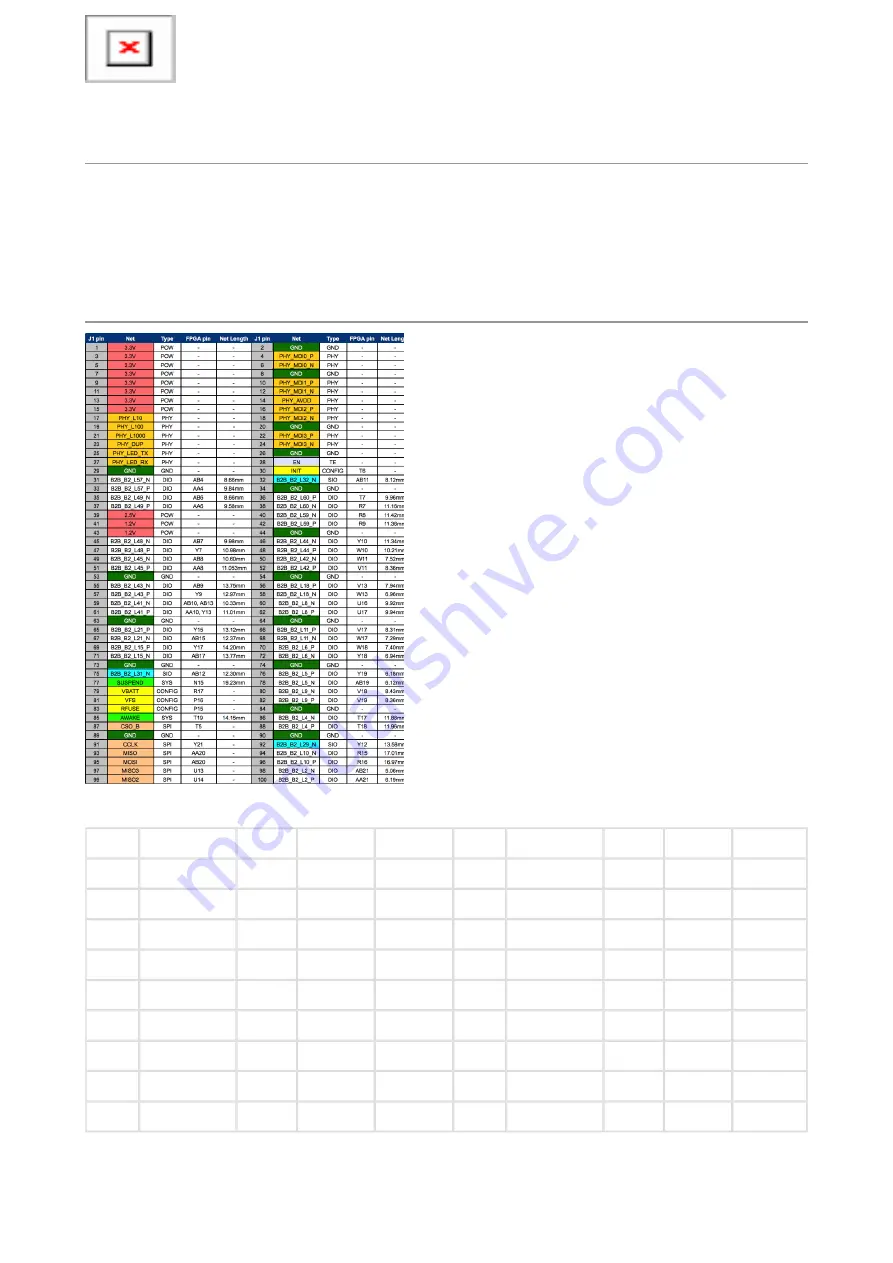

J1 Pin-out

J1 pin-out

J1 pin

Net

Type

FPGA pin

Net Length

J1 pin

Net

Type

FPGA pin

Net Length

1

3.3V

POW

-

-

2

GND

GND

-

-

3

3.3V

POW

-

-

4

PHY_MDI0_P

PHY

-

-

5

3.3V

POW

-

-

6

PHY_MDI0_N

PHY

-

-

7

3.3V

POW

-

-

8

GND

GND

-

-

9

3.3V

POW

-

-

10

PHY_MDI1_P

PHY

-

-

11

3.3V

POW

-

-

12

PHY_MDI1_N

PHY

-

-

13

3.3V

POW

-

-

14

PHY_AVDD

PHY

-

-

15

3.3V

POW

-

-

16

PHY_MDI2_P

PHY

-

-

17

PHY_L10

PHY

-

-

18

PHY_MDI2_N

PHY

-

-