TE0712 TRM

Revision: V14

Copyright © 2017 Trenz Electronic GmbH

Page of

5

20

http://www.trenz-electronic.de

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

11.

12.

13.

14.

15.

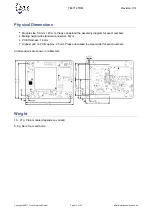

Main Components

Programmable oscillator @25 MHz, SiTime SiT8008, U9

Programmable quad clock generator, Silicon Labs Si5338, U2

10/100 Mbps Ethernet PHY transceiver, Texas Instruments TLK106, U5

Xilinx Artix-7 FPGA XC7A series, U1

32 MByte QSPI Flash memory, Cypress S25FL256S, U4

4 Gbit DDR3 SDRAM, Intelligent Memory IM4G16D3EABG, U15

System Controller CPLD, Lattice Semiconductor MachXO2-256HC, U3

4 Gbit DDR3 SDRAM, Intelligent Memory IM4G16D3EABG, U19

Serial EEPROM, Microchip 11AA02E48, U7

M2

Samtec Razor Beam™ LSHM-150

, J

B2B connector

M1

Samtec Razor Beam™ LSHM-150

, J

B2B connector

M3

Samtec Razor Beam™ LSHM-150

, J

B2B connector

12A Enpirion EN63A0QI PowerSoC DC-DC converter, U14

Green LED (SYSLED1), D1

Red LED (SYSLED2), D2

Initial Delivery State

Programmable unit

Content

Notes

Xilinx Artix-7 FPGA

Not programmed

U1

System Controller CPLD

Programmed

U3

SPI Flash OTP area

Empty

U4

SPI Flash main array

Empty

U4

SPI Flash Quad Enable bit

Set

U4

Microchip 11AA02E48

Globally unique EUI-48 (Ethernet MAC address)

U7