LARA-R2 series - System Integration Manual

UBX-16010573 - R02

Objective Specification

System description

Page 31 of 148

1.6.3

Module reset

LARA-R2 series modules can be properly reset (rebooted) by:

AT+CFUN command (see the

u-blox AT Commands Manual

[2] for more details).

This command causes an “internal” or “software” reset of the module, which is an asynchronous reset of the

module baseband processor. The current parameter settings are saved in the module’s non-volatile memory and

a proper network detach is performed: this is the proper way to reset the modules.

An abrupt hardware reset occurs on LARA-R2 series modules when a low level is applied on the

RESET_N

input

pin for a specific time period. In this case, the current parameter settings are not saved in the module’s non-

volatile memory and a proper network detach is not performed.

It is highly recommended to avoid an abrupt hardware reset of the module by forcing a low level on the

RESET_N

input during modules normal operation: the

RESET_N

line should be set low only if reset or

shutdown via AT commands fails or if the module does not provide a reply to a specific AT command

after a time period longer than the one defined in the

u-blox AT Commands Manual

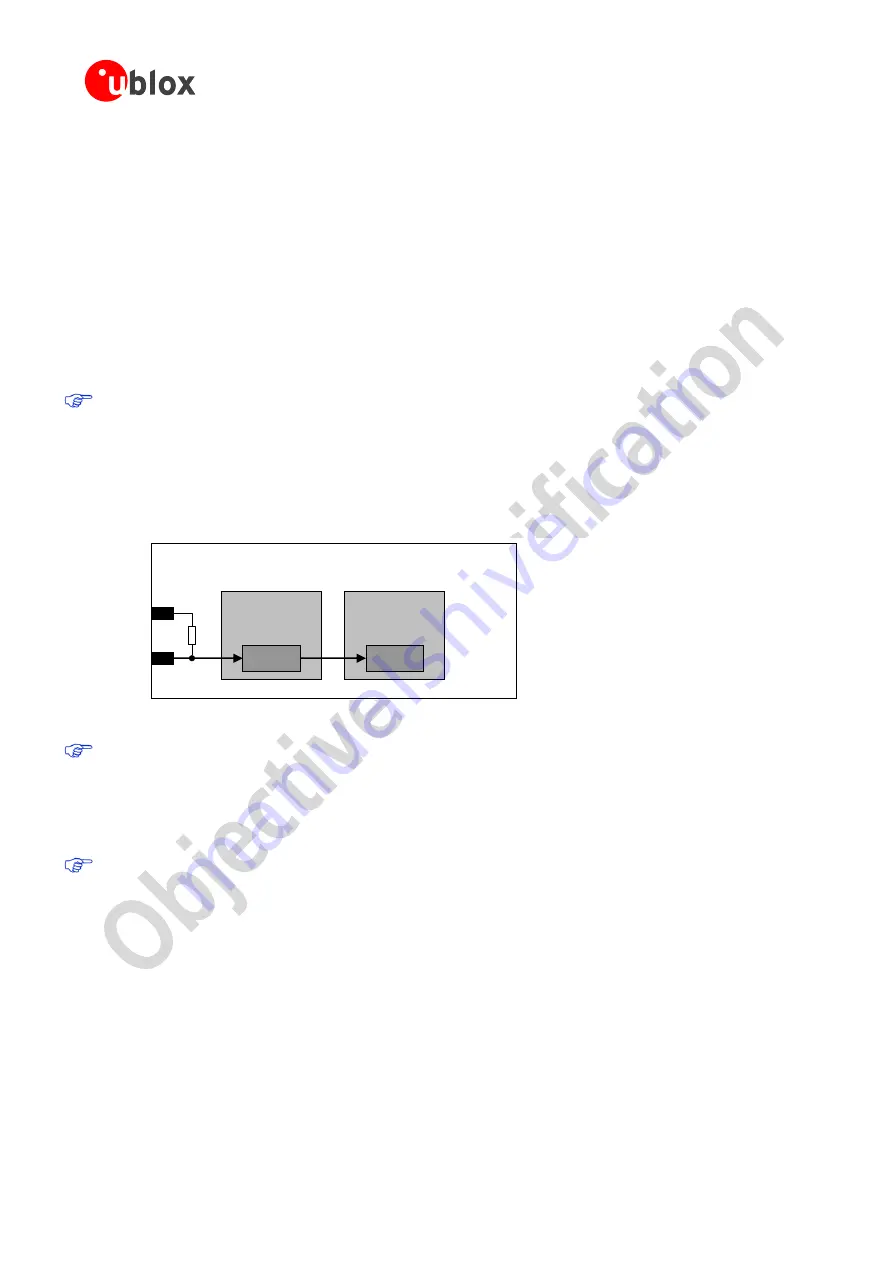

As described in Figure 15, the

RESET_N

input pins are equipped with an internal pull-up to the

V_BCKP

supply.

Baseband

Processor

18

RESET_N

LARA-R2 series

2

V_BCKP

Reset

Power

Management

Reset

10k

Figure 15: LARA-R2 series RESET_N input equivalent circuit description

For more electrical characteristics details see

LARA-R2 series

Data Sheet

1.6.4

Module / host configuration selection

Selection of module / host configuration over

HOST_SELECT

is not supported by “02” product versions.

The modules include one pin (

HOST_SELECT

) to select the module / host application processor configuration:

the pin is available to select, enable, connect, disconnect and subsequently re-connect the HSIC interface.

LARA-R2 series Data Sheet

[1] describes the detailed electrical characteristics of the

HOST_SELECT

pin.