LARA-R2 series - System Integration Manual

UBX-16010573 - R02

Objective Specification

System description

Page 43 of 148

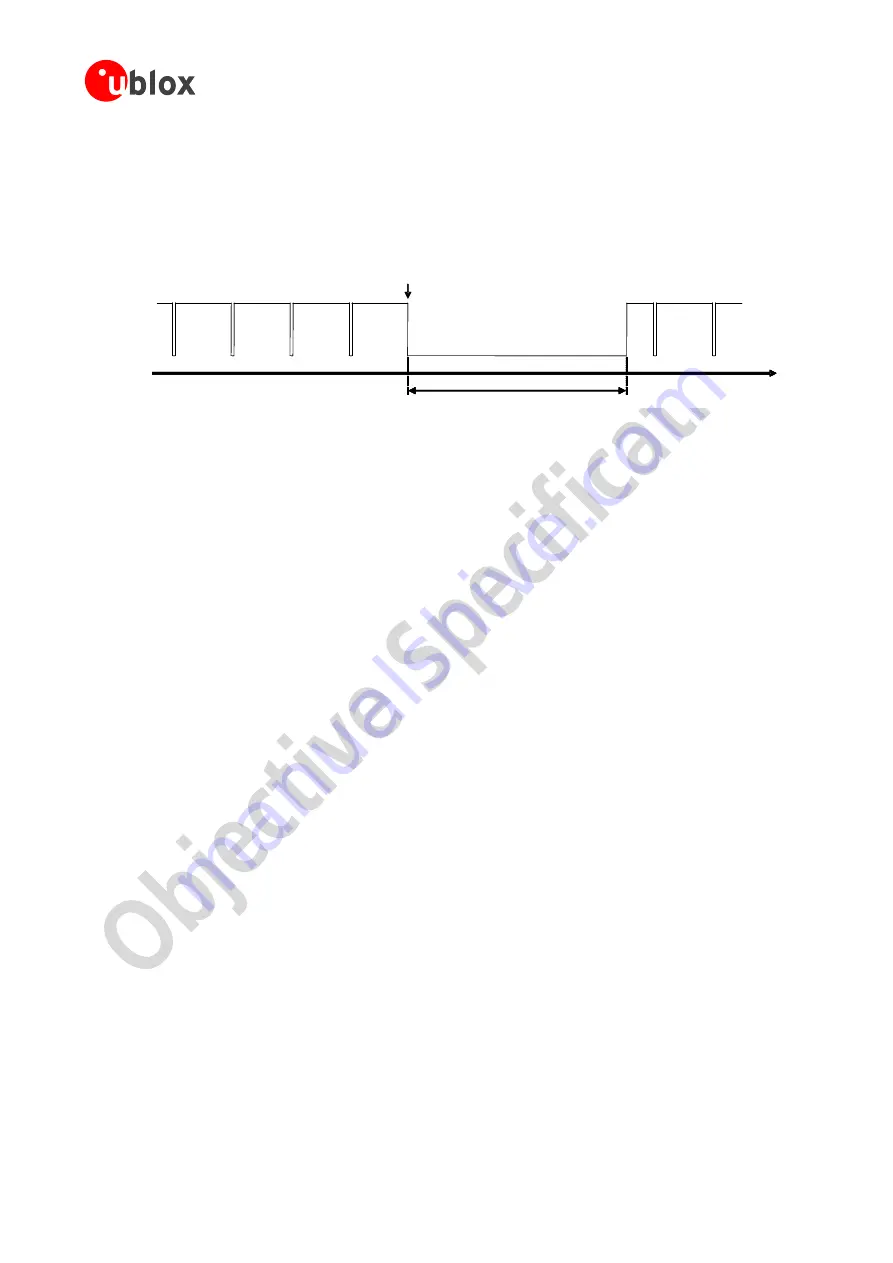

set from 40 2G-frames (i.e. 40 x 4.615 ms = 184 ms) up to 65000 2G-frames (i.e. 65000 x 4.615 ms = 300 s).

Default value is 2000 2G-frames (i.e. 2000 x 4.615 ms = 9.2 s). Every subsequent character received during the

active-mode, resets and restarts the timer; hence the active-mode duration can be extended indefinitely.

The

CTS

output line is driven to the ON or OFF state when the module is either able or not able to accept data

from the DTE over the UART: Figure 19 illustrates the

CTS

output line toggling due to paging reception and data

received over the UART, with AT+UPSV=1 configuration.

time [s]

~9.2 s (default)

Data input

CTS ON

CTS OFF

Figure 19: CTS output pin indicates when module’s UART is enabled (CTS = ON = low level) or disabled (CTS = OFF = high level)

AT+UPSV=2: power saving enabled and controlled by the RTS line

This configuration can only be enabled with the module hardware flow control disabled (i.e. AT&K0 setting).

The UART interface is disabled after the DTE sets the

RTS

line to OFF.

Afterwards, the UART is enabled again, and the module does not enter low power idle-mode, as following:

If an OFF-to-ON transition occurs on the

RTS

input, this causes the UART / module wake-up after ~20 ms:

recognition of subsequent characters is guaranteed only after the complete wake-up, and the UART is kept

enabled as long as the

RTS

input line is set to ON.

If the module needs to transmit some data (e.g. URC), the UART is temporarily enabled to send data

The module automatically enters the low power idle-mode whenever possible but it wakes up to active-mode

according to any required activity related to the network (e.g. for the periodic paging reception described in

section 1.5.1.4, or for any other required RF transmission / reception) or any other required activity related to the

module functions / interfaces (including the UART itself).

AT+UPSV=3: power saving enabled and controlled by the DTR line

The UART interface is disabled after the DTE sets the

DTR

line to OFF.

Afterwards, the UART is enabled again, and the module does not enter low power idle-mode, as following:

If an OFF-to-ON transition occurs on the

DTR

input, this causes the UART / module wake-up after ~20 ms:

recognition of subsequent characters is guaranteed only after the complete wake-up, and the UART is kept

enabled as long as the

DTR

input line is set to ON

If the module needs to transmit some data (e.g. URC), the UART is temporarily enabled to send data

The module automatically enters the low power idle-mode whenever possible but it wakes up to active-mode

according to any required activity related to the network (e.g. for the periodic paging reception described in

section 1.5.1.4, or for any other required RF signal transmission or reception) or any other required activity

related to the functions / interfaces of the module.

The AT+UPSV=3 configuration can be enabled regardless the flow control setting on UART. In particular, the HW

flow control can be enabled (AT&K3) or disabled (AT&K0) on UART during this configuration. In both cases, with

the AT+UPSV=3 configuration, the

CTS

line indicates when the module is either able or not able to accept data

from the DTE over the UART.

When the AT+UPSV=3 configuration is enabled, the

DTR

input line can still be used by the DTE to control the

module behavior according to AT&D command configuration (see

u-blox AT commands Manual