LEON-G100 / LEON-G200 - System Integration Manual

GSM.G1-HW-09002-G3

Preliminary

System description

Page 67 of 125

LEON-G100 /

LEON-G200

3.0V Digital

Audio Device

I2S_TXD (Output)

I2S_CLK (Input)

I2S_RXD (Input)

I2S_WA (Input)

I2S_RXD

I2S_CLK

I2S_TXD

I2S_WA

29

28

27

26

0

Ω

0

Ω

TP

TP

0

Ω

0

Ω

TP

TP

GND

GND

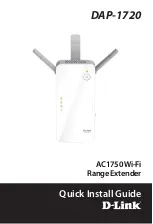

Figure 40: Digital audio interface application circuit

Any external signal connected to the digital audio interface must be tri-stated when the module is in

power-down mode and must be tri-stated during the module power-on sequence (at least for 1500 ms

after the start-up event). If the external signals connected to the digital audio interface cannot be

tri-stated, insert a multi channel digital switch (e.g. Texas Instruments SN74CB3Q16244, TS5A3159, or

TS5A63157) between the two-circuit connections and set to high impedance when the module is in

power down mode and during the module power-on sequence.

If I

2

S pins are not used, they can be left floating on the application board.

For debug purposes, include a test point at each I2S pin also if the digital audio interface is not used.

1.10.2.1

PCM mode

In PCM mode

I2S_TX

and

I2S_RX

are respectively parallel to the analog front end

I2S_RX

and

I2S_TX

as

internal connections to the voice processing system (see Figure 41), so resources available for analog path can be

shared:

Digital filters and digital gains are available in both uplink and downlink direction. They can be configured

using AT commands; refer to the

u-blox AT Commands Manual

Ringer tone and service tone are mixed on the TX path when active (downlink)

The HF algorithm acts on I

2

S path

Main features of the I

2

S interface in PCM mode:

I

2

S runs in PCM - short alignment mode (configurable with AT commands)

Module functions as I

2

S master (

I2S_CLK

and

I2S_WA

signals generated by the module)

I2S_WA

signal always runs at 8 kHz

I2S_WA

toggles high for 1 or 2 CLK cycles of synchronism (configurable), then toggles low for 16 CLK

cycles of sample width. Frame length can be 1 + 16 = 17 bits or 2 + 16 = 18 bits

I2S_CLK

frequency depends on frame length. Can be 17 x 8 kHz = 136 kHz or 18 x 8 kHz = 144 kHz

I2S_TX

,

I2S_RX

data are 16 bit words with 8 kHz sampling rate, mono. Data are in 2’s complement

notation. MSB is transmitted first

When

I2S_WA

toggles high, first synchronization bit is always low. Second synchronism bit (present only in

case of 2 bit long

I2S_WA

configuration) is MSB of the transmitted word (MSB is transmitted twice in this

case)

I2S_TX

changes on

I2S_CLK

rising edge,

I2S_RX

changes on

I2S_CLK

falling edge