NEO-D9S - Integration manual

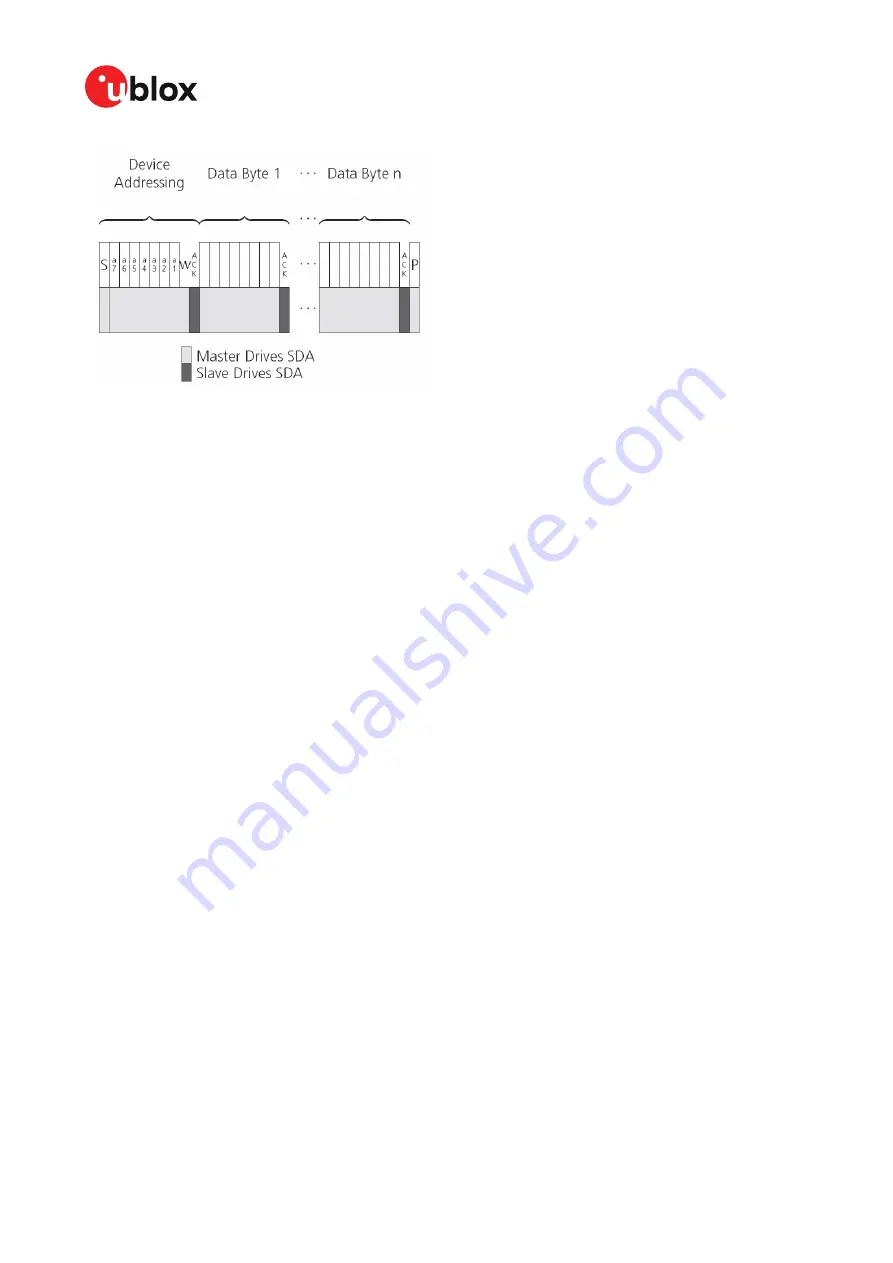

Figure 8: I2C write access

3.2.3 SPI interface

NEO-D9S has an SPI slave interface that can be selected by setting D_SEL = 0. The SPI slave

interface is shared with UART1 and I2C port, the physical pins are same. The SPI pins available are:

• SPI_MISO (TXD)

• SPI_MOSI (RXD)

• SPI_CS_N

• SPI_CLK

See more information about communication interface selection from the

section.

The SPI interface is designed to allow communication to a host CPU. The interface can be operated

in slave mode only.

3.2.3.1 Read access

As the register mode is not implemented for the SPI port, only the UBX/NMEA message stream is

provided. This stream is accessed using the back-to-back read and write access (see section

below). When no data is available to be written to the receiver,

MOSI

should be held logic high, i.e. all bytes written to the receiver are set to 0xFF.

To prevent the receiver from being busy parsing incoming data, the parsing process is stopped after

50 subsequent bytes containing 0xFF. The parsing process is re-enabled with the first byte not equal

to 0xFF.

If the receiver has no more data to send, it sets

MISO

to logic high, i.e. all bytes transmitted decode

to 0xFF. An efficient parser in the host will ignore all 0xFF bytes which are not part of a message and

will resume data processing as soon as the first byte not equal to 0xFF is received.

3.2.3.2 Back-to-back read and write access

The receiver does not provide any write access except for writing UBX and NMEA messages to

the receiver, such as configuration or aiding data. For every byte written to the receiver, a byte will

simultaneously be read from the receiver. While the master writes to

MOSI

, at the same time it needs

to read from

MISO

, as any pending data will be output by the receiver with this access. The data

on

MISO

represents the results from a current address read, returning 0xFF when no more data is

available.

UBX-19026111 - R07

3 Receiver functionality

Page 15 of 52

C1-Public