VAR-320SBC Reference Guide

Copyright © 2008 Variscite

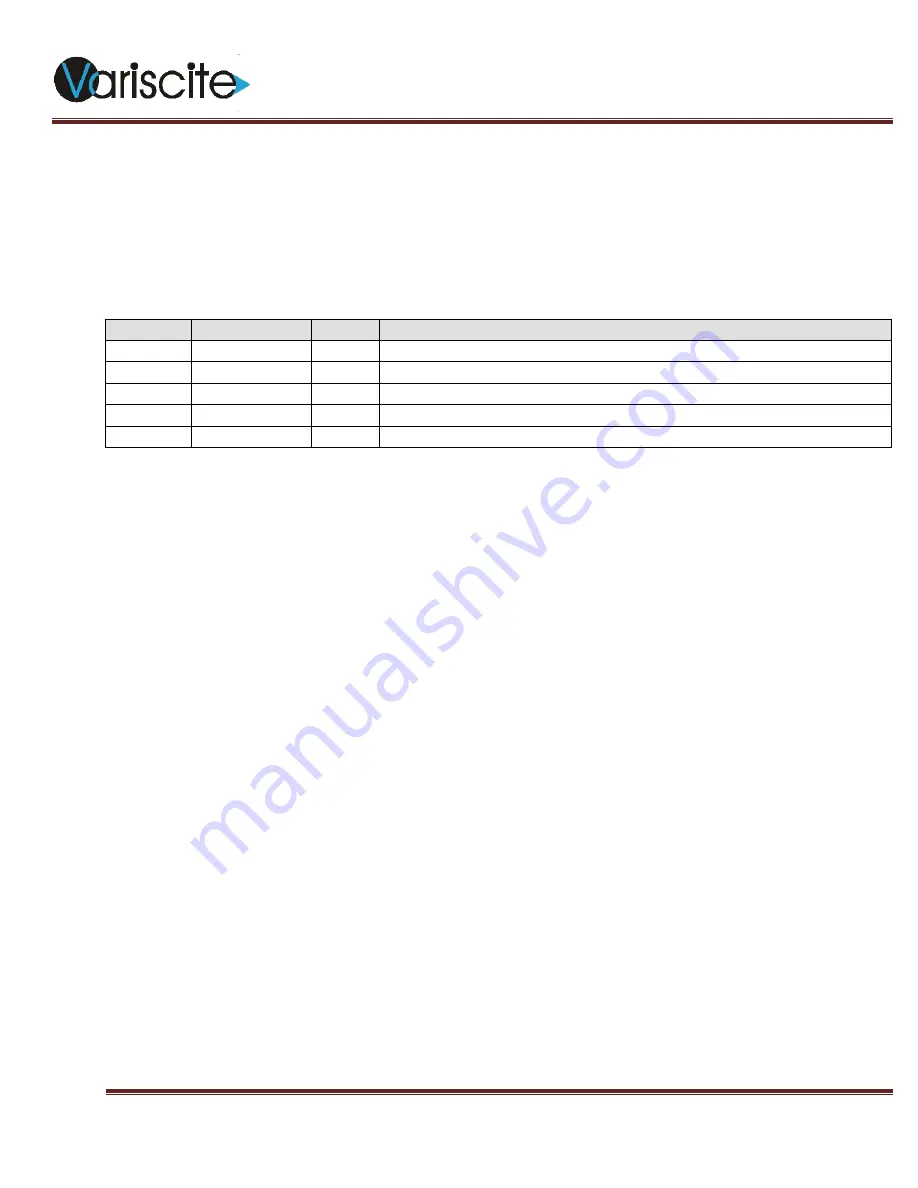

4.6. JTAG Port

JTAG provides a way of driving and sampling the external pins of the device regardless of the

core state, as well as a mechanism for device debug. JTAG logic includes a test-access port

(TAP) controller, TAP pins, an instruction register, and Test Data registers (TDRs). The JTAG

interface is controlled through five dedicated TAP pins that interface to the TAP controller: TDI,

TMS, TCK, nTRST, and TDO.

Signal

Pin number Type

Description

NTRST P2-128

I

JTAG

Test

Reset

TDI

P2-130

I

JTAG Serial data input

TMS P2-132 I JTAG

Test Mode Select

TDO

P2-136

O

JTAG Serial data output

TCK P2-138 I JTAG

Test

Clock

19