FPGA Registers

EPU-4562 Programmer’s Reference Manual

34

UART1CR – UART1 Control Register (COM1)

Reset type is Platform.

Note:

The BIOS (via ACPI) may modify this register when in an ACPI-capable operating

system. The register can be read for status purposes but do not write to it unless you are using a

non-ACPI operating system.

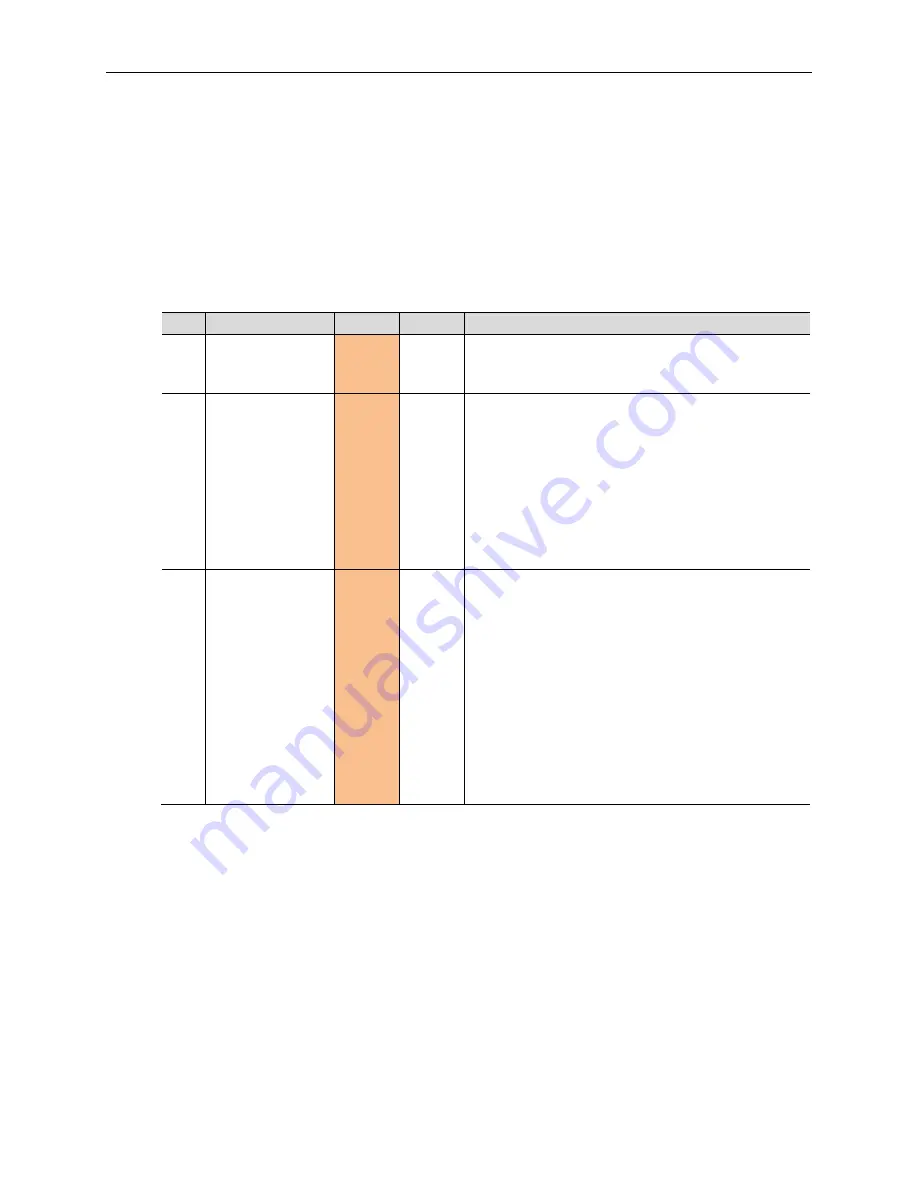

Table 43: UART1CR – UART1 Control Register (COM1)

Bits

Identifier

Access

Default

Description

7

IRQEN

R/W

0

UART interrupt enable/disable:

0 – Interrupts disabled

1 – Interrupts enabled

6-4

IRQSEL(2:0)

R/W

001

UART interrupt IRQ select in LPC SERIRQ:

000 – IRQ3

001 – IRQ4

[

COM1 Default]

010 – IRQ5

011 – IRQ10

100 – IRQ6

101 – IRQ7

110 – IRQ9

111 – IRQ11

3-0

UART1_BASE(3:0)

R/W

0000

UART Base Address:

0000 - 3F8h

[

COM1 Default]

0001 - 2F8h

0010 - 3E8h

0011 - 2E8h

0100 - 200h

0101 - 220h

0110 - 228h

0111 - 338h

1000 - 238h

1001 - 338h

1010-1111

[

These values are reserved; do not use.]