Page 14 of 32

V1682OPMA.doc

17 February, 2005

4. MAKING MEASUREMENTS

4.1 I

NTRODUCTION

The V1682 VALID reader, when fed with video and audio signals from the V1681 VALID generator,

has the capability to measure audio delay relative to video, audio level, and will identify the channel

cross-overs, L/R swaps, and channel inversions. The time-marked video signal from the V1681 is

rugged enough to pass unscathed through almost any video processing or transport medium,

including ARCs, standards converters, compression links, noise reducers and noisy satellite links.

4.2 V

IDEO

I

NPUT

The V1682 accepts a CCIR601 SDI input through on of its two** inputs. Selection of the video input

is done under the

VID OSD > SDI Src

menu option. If only one input is available, this control is not

adjustable.

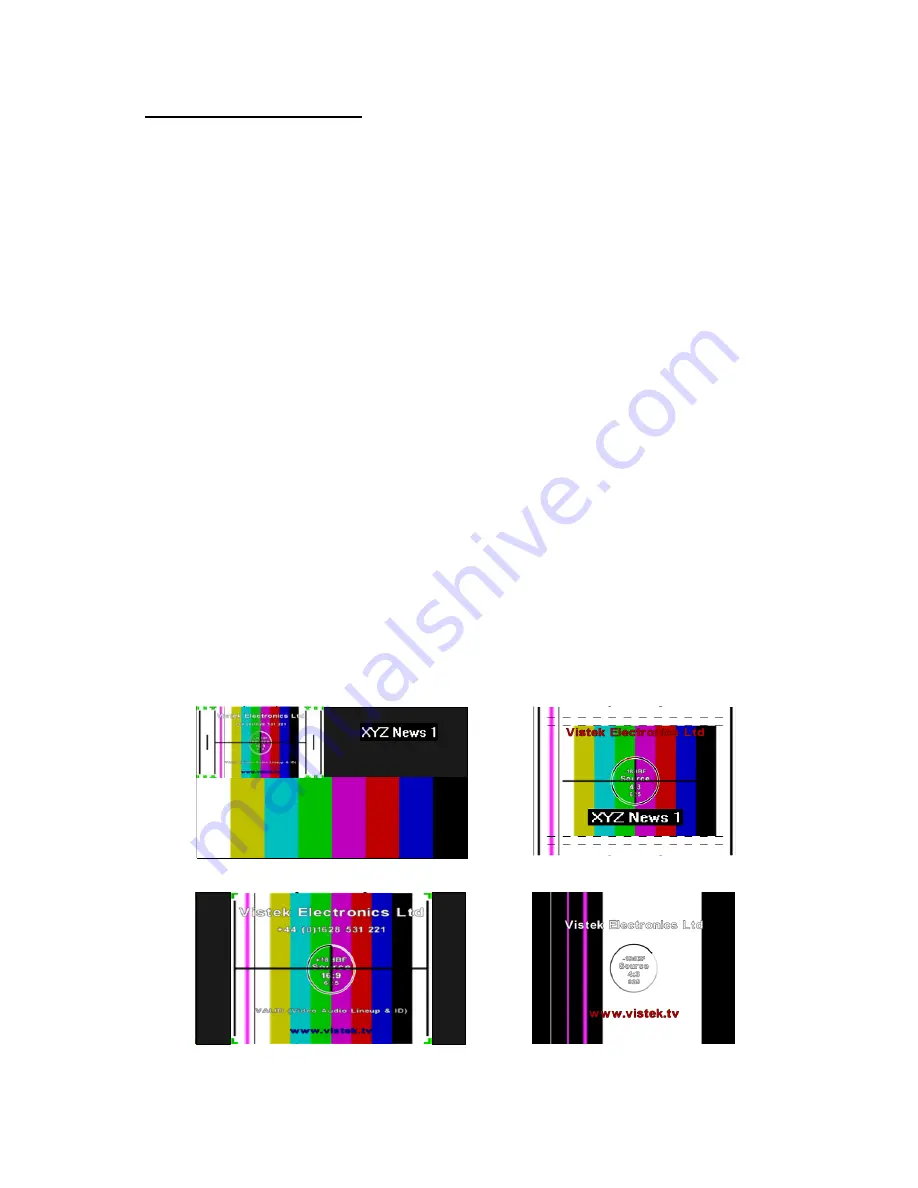

In order to make correct timing measurements, the input video must contain a continuous signal

from a V1681 VALID generator. The V1682 is capable of making timing measurements even when

the video from the V1681 has been reduced to any size down to ¼ screen, with any additional

stationary content in the picture, as long as all but the VALID test signal is stationary (Figure 4.1a).

The VALID system will NOT work correctly if any significant movement has been superimposed

picture received by the V1682, but stationary captions / logos are allowed (Figure 4.1b).

The system is not dependent on background test pattern, so any of the test patterns generated by

the V1681 generator are suitable for measurements (e.g. Figure 4.1d), except for the pluge signal

which may give unreliable results due to the low luminance level.

The system is also tolerant of very low signal levels (as low as –12dB), and high levels of noise.

The VALID system Is designed to work through cross-standards, so even if the generator is working

in a 625 line format, the receiver will measure correctly after standard conversion to 525 (or vica-

versa).

** The second SDI input is optional and only available with the correct link settings, see Sec 2.5.2 .

(a)

(b)

(d)

(c)

Figure 4.1 – Examples of acceptable VALID test signals