16

6000-2 & -3 User Guide, Rev E

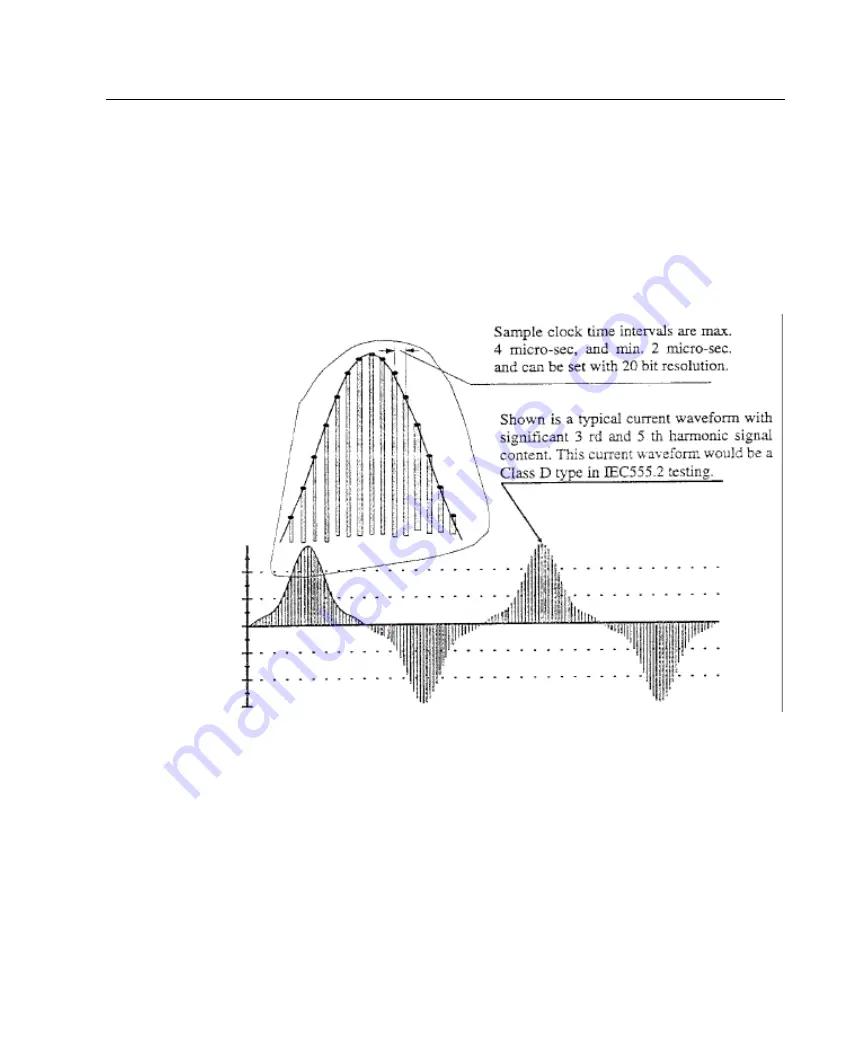

frequency is settable with 20-bit resolution over a 2:1 range of frequencies. This

clock signal is available to all amplitude DSP systems on one of three such signal

lines. If desired by the central processor, the supervisory processor can “link” this

frequency to that of either of its measured input frequencies. The form of the sample

clock is such that the individual sample-to-sample clock period can vary by up to

1%, however, the average over any 256 sample period is always within 1ppm of the

set value. This “jittered” sampling ensures that no input signal component can be

synchronous to the amplitude system’s sample rate, removing the anomalous effects

that occur when this happens.

Figure 3. Sample Clock

Filter Clock Generation

Under the direction of the central processor, the supervisory DSP controls circuitry

contained in an ASIC which generates a digital clock signal whose frequency is

selectable in 1.2:1 steps over 4.5 decades of frequencies. This clock signal is

available to all amplitude DSP systems on one of three such signal lines.

Summary of Contents for Xitron 6000-2

Page 1: ...USER S GUIDE 6000 2 6000 3 Phase Angle Voltmeters...

Page 2: ......

Page 36: ...36 6000 2 3 User Guide Rev E...

Page 86: ...86 6000 2 3 User Guide Rev E...

Page 94: ...94 6000 2 3 User Guide Rev E...

Page 101: ...Appendix B 101...