VX1828B

Preliminary Datasheet

Video Processor for Middle Size LCD Panel

P.26/P.64

V1.0 050420

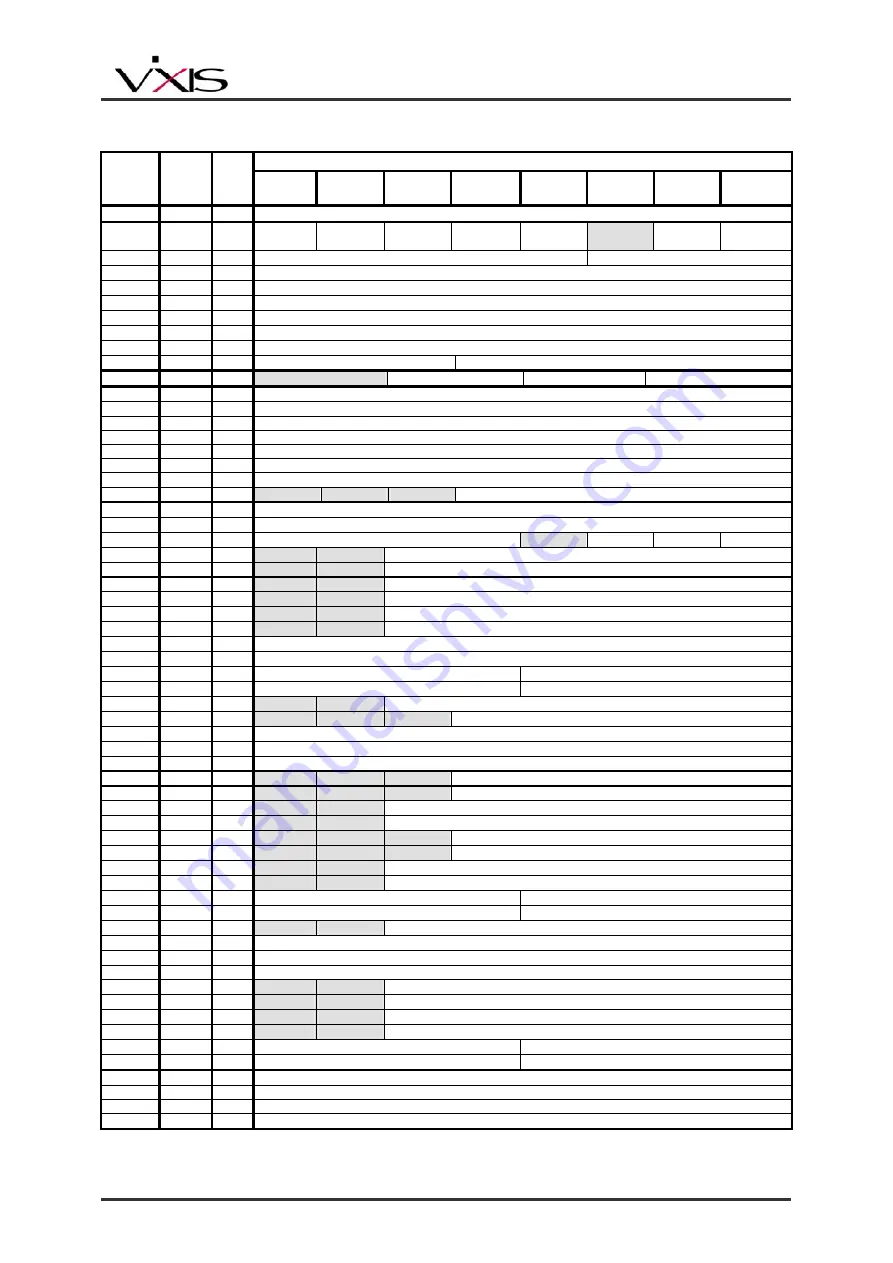

Bit Map

Addr.

(Hex)

Name

Def.

(Hex

)

7 6 5 4 3 2 1 0

39 TC42

49

RATE2_PARA_A[7:0]

3A OS7

00

AOUT_

OFF

VOCLKP

HSYNCP

VSYNCP

VOCLKD2

-

OTRI_

CLK

OTRI

3B OS8

A9

HS_WIDTH

VS_WIDTH

3C OS9

94

HSHIFT

3D OSA

00

VSHIFT

3E OSB

00

BOTTOM_MASK

3F OSC

00

TOP_MASK

40 OSD

00

LEFT_MASK

41 OSE

00

RIGHT_MASK

42 OSF

00

PG_SEL

PG_LEVEL

43 PWM0

00

-

PWM_SEL1 PWM_SEL2 PWM_SEL3

44 TC43

4A

RATE2_PARAM_A[15:8]

49 TC44

02

RATE2_PARAM_A[23:16]

4A TC45

00

RATE2_PARAM_A[31:24]

4B TC46

49

RAET2_PARAM_B[7:0]

4C TC47

48

RATE2_PARAM_B[15:8]

4D TC48

02

RATE2_PARAM_B[23:16]

4E TC49

00

RATE2_PARAM_B[31:24]

4F TC50

1F -

-

-

RATE3_CNT_N[4:0]

50 OSD0

00

OSD_ADDR

51 OSD1

00

OSD_DATA

52 OSD2

E0

OSD_ALPHA

-

OSDT_EN OSDC_EN OSDB_EN

53 OSD3

08 -

-

OSD_BLINK

54 OSD4

04 -

-

OSDT_SIZEX

55 OSD5

00 -

-

OSDT_HLSTART

56 OSD6

00 -

-

OSDT_HLSTOP

57 OSD7

00 -

-

OSDT_BLSTART

58 OSD8

00 -

-

OSDT_BLSTOP

59 OSD9

28

OSDT_POSX

5A OSD10

10

OSDT_POSY

5B OSD11

82

OSDT_BGCLR

OSDT_FGCLR

5C OSD12

B4

OSDT_HLBGCLR

OSDT_HLFGCLR

5D OSD13

10

-

-

OSDC_SIZEX

5E OSD14

08

-

-

-

OSDC_SIZEY

5F OSD15

04

OSDC_START

60 OSD16

40

OSDC_POSX

61 OSD17

1A

OSDC_POSY

62 OSD18

00

-

-

-

OSDC_HLY_START

63 OSD19

00

-

-

-

OSDC_HLY_STOP

64 OSD20

01

-

-

OSDC_HLX_START

65 OSD21

00

-

-

OSDC_HLX_STOP

66 OSD22

00

-

-

-

OSDC_BLY_START

67 OSD23

00

-

-

-

OSDC_BLY_STOP

68 OSD24

01

-

-

OSDC_BLX_START

69 OSD25

00

-

-

OSDC_BLX_STOP

6A OSD26

1F

OSDC_BGCLR

OSDC_FGCLR

6B OSD27

6a

OSDC_HLBGCLR

OSDC_HLFGCLR

6C OSD28

08

-

-

OSDB_SIZEX

6D OSD29

84

OSDB_START

6E OSD30

88

OSDB_POSX

6F OSD31

6C

OSDB_POSY

70 OSD32

00

-

-

OSDB_HLSTART

71 OSD33

00

-

-

OSDB_HLSTOP

72 OSD34

00

-

-

OSDB_BLSTART

73 OSD35

00

-

-

OSDB_BLSTOP

74 OSD36

79

OSDB_BGCLR

OSDB_FGCLR

75 OSD37

3E

OSDB_HLBGCLR

OSDB_HLFGCLR

76 TC51

55

RATE3_PARAM_A[7:0]

77 TC52

55

RATE3_PARAM_A[15:8]

78 TC53

55

RATE3_PARAM_A[23:16]

79 TC54

55

RATE3_PARAM_A[31:24]