VX1828B

Preliminary Datasheet

Video Processor for Middle Size LCD Panel

P.54/P.64

V1.0 050420

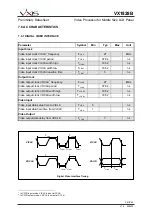

37 TC39

00

RATE1_PARAM_B[31:24]

CPH_MODE

001 CPH consists of rate1 only

011

CPH switches between rate1 and rate2

111

CPH switches between rate1, rate2 and rate3

RATE1_CNT_N

parameter to set rate1

RATE1_PARAM_A

parameter to set rate1

RATE1_PARAM_A

parameter to set rate1

Bit Map

Addr.

(Hex)

Name

Def.

(Hex)

7 6 5 4 3 2 1 0

38 TC41

13 CPH_DLY[1:0]

-

RATE2_CNT_N

39 TC42

49

RATE2_PARAM_A[7:0]

44 TC43

4A

RATE2_PARAM_A[15:8]

49 TC44

02

RATE2_PARAM_A[23:16]

4A TC45 00

RATE2_PARAM_A[31:24]

4B TC46 49

RATE2_PARAM_B[7:0]

4C TC47 48

RATE2_PARAM_B[15:8]

4D TC48 02

RATE2_PARAM_B[24:16]

4E TC49 00

RATE2_PARAM_B[31:24]

CPH_DLY[1:0]

To set clock phases of CPH2 and CPH3

RATE2_CNT_N

parameter to set rate2

RATE2_PARAM_A

parameter to set rate2

RATE2_PARAM_A

parameter to set rate2

Bit Map

Addr.

(Hex)

Name

Def.

(Hex)

7 6 5 4 3 2 1 0

4F TC50

1F -

-

-

RATE3_CNT_N

76 TC51

55

RATE3_PARAM_A[7:0]

77 TC52

55

RATE3_PARAM_A[15:8]

78 TC53

55

RATE3_PARAM_A[23:16]

79 TC54

55

RATE3_PARAM_A[31:24]

9C TC55 00

RATE3_PARAM_B[7:0]

9D TC56 00

RATE3_PARAM_B[15:8]

9E TC57 00

RATE3_PARAM_B[24:16]

9F TC58

00

RATE3_PARAM_B[31:24]

RATE3_CNT_N

parameter to set rate3

RATE3_PARAM_A

parameter to set rate3

RATE3_PARAM_A

parameter to set rate3