VX1828B

Preliminary Datasheet

Video Processor for Middle Size LCD Panel

P.55/P.64

V1.0 050420

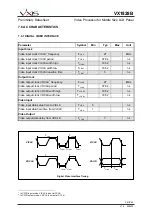

6.2.15 STATUS REGISTERS

Bit Map

Addr.

(Hex)

Name

Def.

(Hex)

7 6 5 4 3 2 1 0

D0 Status -

-

-

AGC_STATUS

D1 Status -

DAGC_STATUS

D2 Status -

BLKLEV_STATUS

D3 Status -

NOISE

MORE

PHALT IS443 VPRES

MODE

[1:0] FINEAGC

MVVALID

D4 Status -

CAGC_STATUS

D5 Status -

CCPRES CC525

-

-

-

-

-

LLOCK

AGC_STATUS

Controls gain of analog composite/luma and chroma inputs

DAGC_STATUS

Internal digital automatic gain control value

BLKLEV_STATUS

Black level. 0 means no change. (ref: 7’b1000110 = 70d)

NOISE_MORE

Video noise detection. 1 represents there is more noise

PHALT

Phase switching signal of PAL signal

IS443

Carrier frequency detection

0

3.58

MHz

1

4.43

MHz

VPRES

Coarse lock status. Set when sync of proper height and duration

has been detected on 32 successive lines; reset if sync is not

detected on 32 successive lines.

0

Unlock

1

Locked

MODE

0 PAL (Combination N)

1 PAL (B, D, G, H, I, N)

2

PAL

(M)

3

NTSC

FINEAGC

Automatic gain control stability indication

0

Unstable

1

Stable

MVVALID

MacroVision protect detection

0 MacroVision protect waveform exist

1 None MacroVision protect waveform

CAGC_STATUS

Chroma automatic gain control value

CCPRES

CCIR656 input video present, only available when ccir_in_en set

CC525

0 CCIR656 input video is 525-line format (df.)

1 CCIR656 input video is 625-line format

LLOCK

Indication of successive lines

0 Successive lines available exist

1 No successive lines available