101019

OPERATIONS MANUAL PPM-LX800-G

11

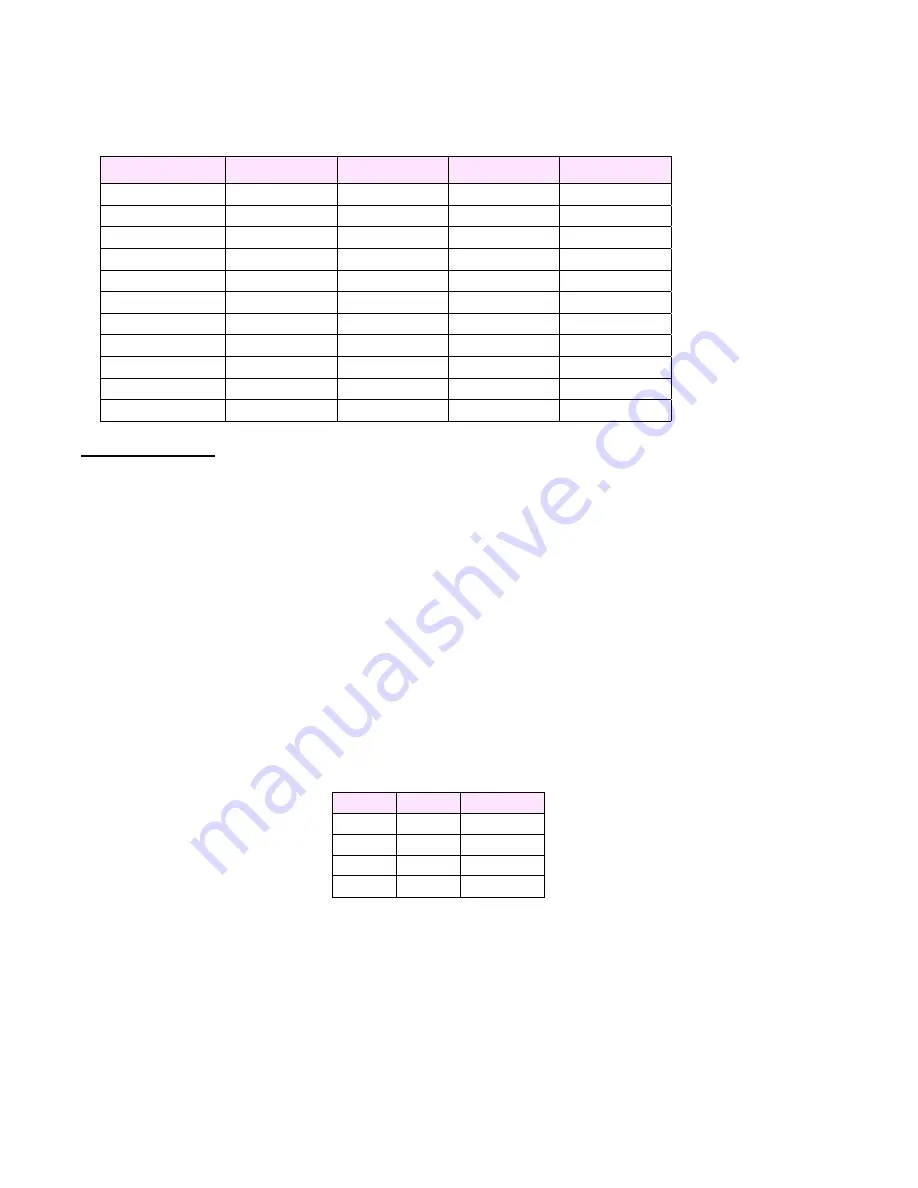

WS16C48 Compatible Digital I/O

This device provides 16 lines of digital I/O. The following table summarized the registers and the

text that follows provides details on each of the internal registers.

Register Details

Port 0 through 1 I/O –

Each I/O bit in each of the six ports can be individually programmed

for input or output. Writing a

0

to a bit position causes the corresponding output pin to go to a

high-impedance state (pulled high by external 10 KΩ resistors). This allows it to be used as an

input. When used in the input mode, a read reflects the inverted state of the I/O pin, such that

a high on the pin will read as a

0

in the register. Writing a

1

to a bit position causes that output

pin to sink current (up to 12 mA), effectively pulling it low.

INT_PENDING –

This read-only register reflects the combined state of the INT_ID0 through

INT_ID2 registers. When any of the lower three bits are set, it indicates that an interrupt is

pending on the I/O port corresponding to the bit position(s) that are set. Reading this register

allows an Interrupt Service Routine to quickly determine if any interrupts are pending and which

I/O port has a pending interrupt.

PAGE/LOCK –

This register serves two purposes. The upper two bits select the register page in

use as shown here:

Bits 5-0 allow for locking the I/O ports. A

1

written to the I/O port position will prohibit further

writes to the corresponding I/O port.

I/O Address

Offset

Page 0

Page 1

Page 2

Page 3

00H

Port 0 I/O

Port 0 I/O

Port 0 I/O

Port 0 I/O

01H

Port 1 I/O

Port 1 I/O

Port 1 I/O

Port 1 I/O

02H

RESERVED

RESERVED

RESERVED

RESERVED

03H

RESERVED

RESERVED

RESERVED

RESERVED

04H

RESERVED

RESERVED

RESERVED

RESERVED

05H

RESERVED

RESERVED

RESERVED

RESERVED

06H

Int_ Pending

Int_ Pending

Int_ Pending

Int_ Pending

07H

Page/Lock

Page/Lock

Page/Lock

Page/Lock

08H

N/A

Pol_0

Enab_0

Int_ID0

09H

N/A

Pol_1

Enab_1

Int_ID1

0AH

N/A

Pol_2

Enab_2

Int_ID2

D7

D6

Page

0

0

Page 0

0

1

Page 1

1

0

Page 2

1

1

Page 3