WIZ127SR User’s Manual

37

4.5.2.

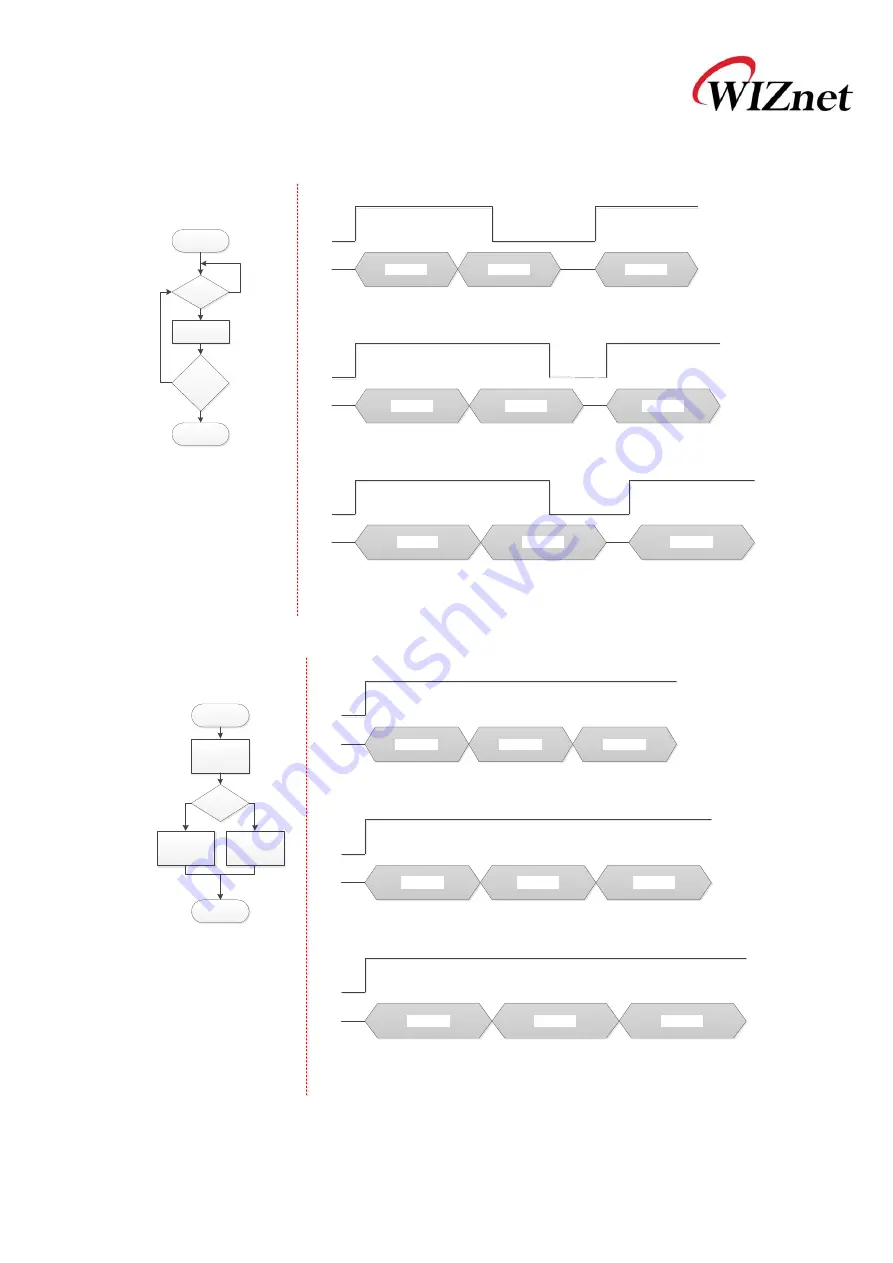

DTR/DSR mode Timing Diagram

Start

Check DTR

Send a byte

Is there

any data

to send?

End

No

Yes

It is fine to send

Do not send

8 bits Data

7 bits Data

9 bits Data

7 bits Data

7 bits Data

8 bits Data

9 bits Data

8 bits Data

9 bits Data

DTR

Tx

DTR

Tx

DTR

Tx

DTR

(Data Terminal Ready)

Figure 10. DTR signal timing diagram under DSR/DTR mode

Start

Successful

Initialize?

Set DSR to

HIGH

End

Yes

8 bits Data

7 bits Data

9 bits Data

7 bits Data

7 bits Data

8 bits Data

9 bits Data

8 bits Data

9 bits Data

DSR

Rx

DSR

Rx

DSR

Rx

Set DSR to

LOW

Device

Initialize

DSR

(Data Set Ready)

No

Figure 11. DSR signal Timing Diagram under DSR/DTR mode