Hardware Reference Guide

SST-DN3-PCI-1 and SST-DN3-PCI-2

34

Hardware

Register

Details

©2004 Woodhead Software & Electronics, Division of Woodhead Canada Limited

Document Edition: 1.1, Document #: 715-0083, Template Edition: 1.1, Template #: QMS-06-045

Use, duplication or disclosure of this document or any of the information contained herein is subject to the restrictions on page ii of this document.

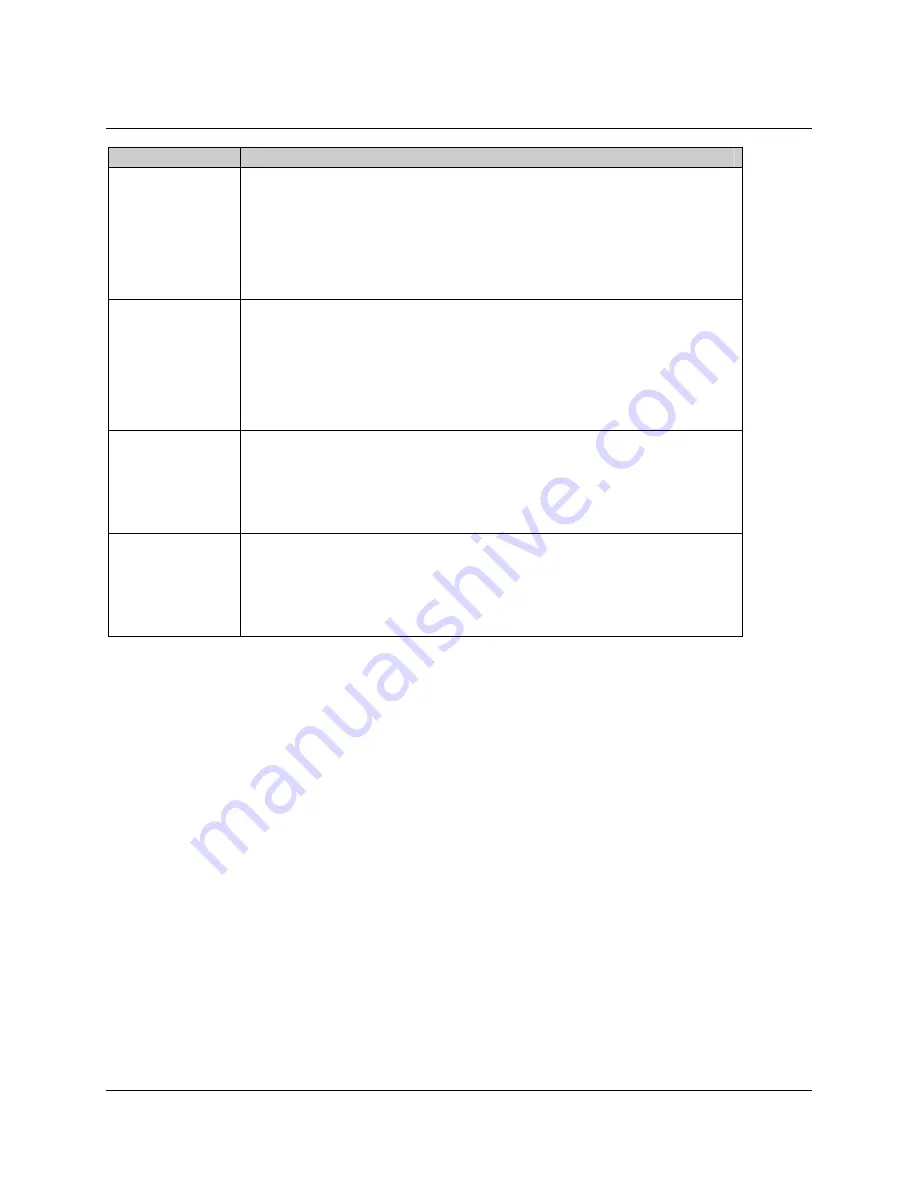

Bit Name

Description

HostIrq1

•

This bit is used by the channel’s processor to indicate that the channel generated an

interrupt. If IntEn is set to 1, this also means that the channel generated a physical

interrupt on the PCI bus.

•

Writing 1 acknowledges the interrupt and clears it

•

Writing 0 has no effect

•

Reading 1 indicates interrupt in progress

•

Reading 0 indicates interrupt complete

HostIrq0

•

This bit is used by the channel’s processor to indicate that the channel generated an

interrupt. If IntEn is set to 1, this also means that the channel generated a physical

interrupt on the PCI bus.

•

Writing 1 acknowledges the interrupt and clears it

•

Writing 0 has no effect

•

Reading 1 indicates interrupt in progress

•

Reading 0 indicates interrupt complete

CardIrq1

This bit is used by the host to send interrupts to interrupt flag 1 of the channel’s processor.

•

Writing 1 generates an interrupt

•

Writing 0 has no effect

•

Reading 1 indicates interrupt in progress

•

Reading 0 indicates interrupt complete

CardIrq0

This bit is used by the host to send interrupts to interrupt flag 0 of the channel’s processor.

•

Writing 1 generates an interrupt

•

Writing 0 has no effect

•

Reading 1 indicates interrupt in progress

•

Reading 0 indicates interrupt complete

3.3.3 AddrMatch Register

This register is reserved.

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com