Bit 4 - Execution Error (Abarbeitungsfehler). Wird gesetzt, wenn beim Versuch der Abarbeitung

eines vollständig verarbeiteten Befehls ein Fehler festgestellt wird. Die entsprechende

Fehlernummer wird im Execution Error Register aufgezeichnet.

1- 99 Gibt an dass ein Hardware-Fehler aufgetreten ist.

116

Die Setup-Daten wurden abgerufen, der genannte Speicher enthält jedoch keine

Daten.

117

Die Setup-Daten wurden abgerufen, der genannte Speicher enthält jedoch korrupte

Daten. Dies deutet entweder auf einen Hardware-Fehler oder auf eine zeitweilige

Datenkorruption hin und kann durch erneutes Schreiben der Daten in den Speicher

korrigiert werden.

120

Der mit dem Befehl gesandte numerische Wert war zu groß bzw. zu klein. Gilt auch

für negative Zahlen, wenn nur positive Zahlen gültig sind.

123

Abruf/Speicherung der Setup-Daten von einer unzulässigen Speichernummer aus.

124

Es wurde ein Bereichswechsel angefordert, der jedoch im Rahmen der aktuellen

Einstellungen des Netzgeräts unzulässig ist – weitere Informationen hierzu siehe

Abschnitt „Manuelle Bedienung“.

Bit 3 - „Verify Timeout“ Fehler. Wird gesetzt wenn ein Parameter verifiziert werden soll, der

jeweilige Wert aber nicht innerhalb von 5 Sekunden erreicht ist (, z. B. wenn die

Ausgangsspannung durch einen großen Kondensator am Ausgang verzögert wurde.

Bit 2 - Query Error (Abfragefehler). Wird gesetzt, wenn ein Abfragefehler auftritt. Die

entsprechende Fehlernummer wird im Query Error Register wie folgt aufgezeichnet.

1. Interrupted Error (Unterbrechungsfehler)

2. Deadlock Error (Blockierungsfehler)

3. Unterminated Error („Nicht abgeschlossen“-Fehler)

Bit 1 - Nicht belegt.

Bit 0 - Operation Complete (Vorgang abgeschlossen). Wird als Antwort auf den *OPC-Befehl

gesetzt.

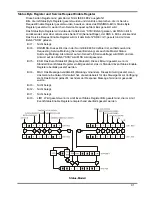

Limit Event Status Register und Limit Event Status Enable Register

Diese beiden Register sind ergänzend zur Norm IEEE 488.2 vorhanden. Sie dienen dazu den

steuernden Rechner über die aktuellen Strom- und Spannungsbegrenzungsbedingungen zu

informieren und die Historie der Schutzauslösebedingungen seit dem letzten Lesevorgang zu

erfassen.

Bits, die im Limit Event Status Register gesetzt wurden und den Bits entsprechen, die im Limit

Event Status Enable Register gesetzt wurden, bewirken dass das LIM1 Bit im Status Byte

Register gesetzt wird.

Das Limit Event Status Register wird mit dem Befehl LSR1? gelesen und gelöscht. Das Limit

Event Status Enable Register wird mit dem Befehl LSE1<nrf> gesetzt und mit dem Befehl LSE1?

gelesen.

Bit 7 - nicht belegt

Bit 6 - nicht belegt

Bit 5 - Wird gesetzt wenn ein Auslöser im Sense-Betrieb aufgetreten ist

Bit 4 - Wird gesetzt wenn der Übertemperaturschutz ausgelöst worden ist

Bit 3 - Wird gesetzt wenn der Überstromschutz ausgelöst worden ist

Bit 2 - Wird gesetzt wenn der Überspannungsschutz ausgelöst worden ist

Bit 1 - Wird gesetzt wenn der Strombegrenzungswert erreicht ist (Konstantstrombetrieb)

Bit 0 - Wird gesetzt wenn der Spannungsbegrenzungswert erreicht ist

(Konstantspannungsbetrieb)

90