FMC XM101 User Guide

17

UG538 (v1.1) September 24, 2010

XM101 Board Technical Description

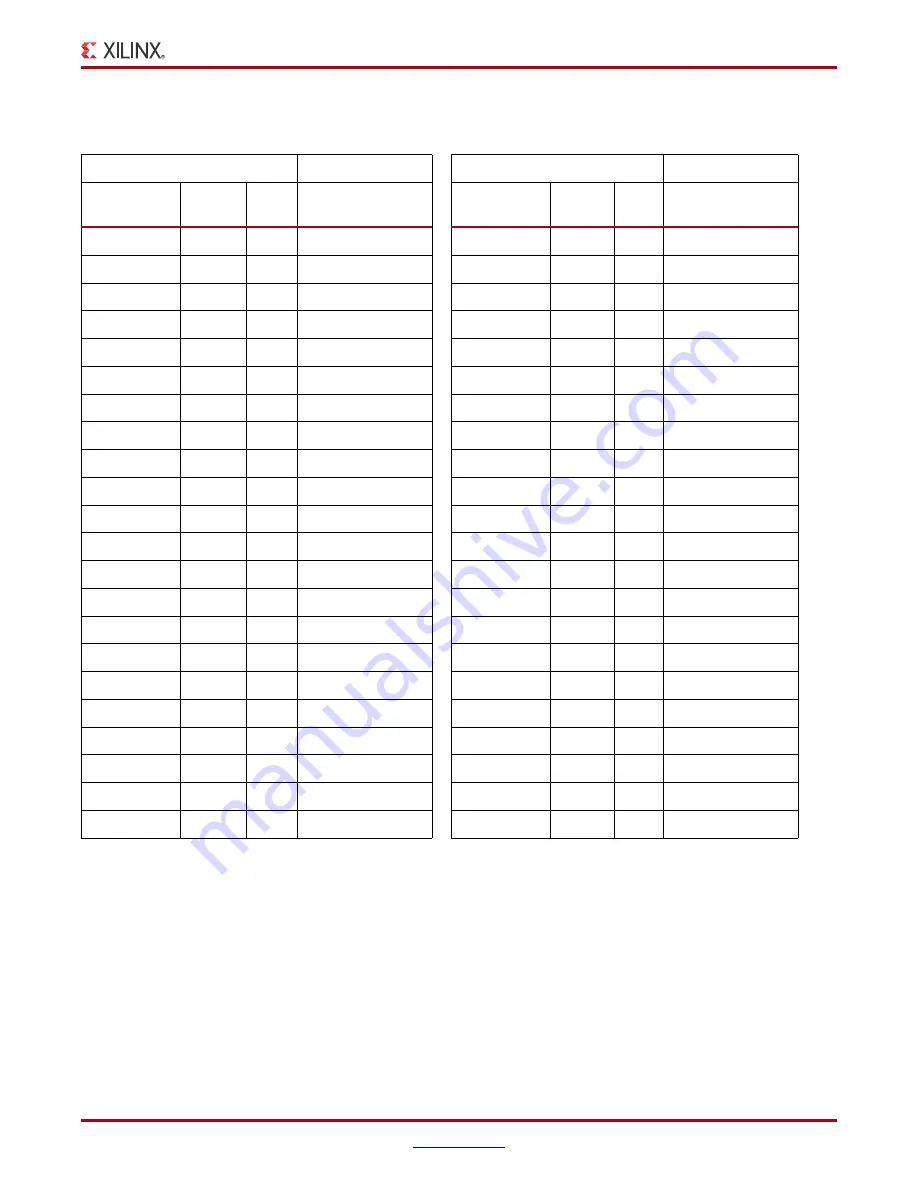

Table 1-6:

P4 QSE3 QSE3 to J1 FMC HPC Connections

P4 Odd Side

J1 FMC Connector

P4 Even Side

J1 FMC Connector

Net Name

Pin

Number

Pin

Name

Pin Number

Net Name

Pin

Number

Pin

Name

Pin Number

HB01_P

1

A1

J24

HB02_P

2

B1

F22

HB01_N

3

A2

J25

HB02_N

4

B2

F23

HB03_P

7

C1

E21

HB04_P

8

D1

F25

HB03_N

9

C2

E22

HB04_N

10

D2

F26

HB05_P

13

E1

E24

HB07_P

14

F1

J27

HB05_N

15

E2

E25

HB07_N

16

F2

J28

HB08_P

19

G1

F28

HB09_P

20

H1

E27

HB08_N

21

G2

F29

HB09_N

22

H2

E28

HB00_CC_P

25

I1

K25

HB06_CC_P

26

J1

K28

HB00_CC_N

27

I2

K26

HB06_CC_N

28

J2

K29

HB10_P

31

K1

K31

HB11_P

32

L1

J30

HB10_N

33

K2

K32

HB11_N

34

L2

J31

HB12_P

37

M1

F31

HB13_P

38

N1

E30

HB12_N

39

M2

F32

HB13_N

40

N2

E31

HB14_P

41

O1

K34

HB15_P

42

P1

J33

HB14_N

43

O2

K35

HB15_N

44

P2

J34

HB16_P

47

Q1

F34

HB17_CC_P

48

R1

K37

HB16_N

49

Q2

F35

HB17_CC_N

50

R2

K38

HB18_P

53

S1

J36

HB19_P

54

T1

E33

HB18_N

55

S2

J37

HB19_N

56

T2

E34

HB20_P

59

U1

F37

(1)

HB21_P

60

V1

E36

(1)

HB20_N

61

U2

F38

(1)

HB21_N

62

V2

E37

(1)

Notes:

1. The ML605 board FMC HPC connector J64 does not support these signals

Summary of Contents for FMC XM101 LVDS QSE

Page 1: ...FMC XM101 LVDS QSE Card User Guide UG538 v1 1 September 24 2010 ...

Page 4: ...4 www xilinx com FMC XM101 User Guide UG538 v1 1 September 24 2010 ...

Page 6: ...6 www xilinx com FMC XM101 User Guide UG538 v1 1 September 24 2010 Preface About This Guide ...

Page 22: ...22 www xilinx com FMC XM101 User Guide UG538 v1 1 September 24 2010 Chapter 1 XM101 ...