Platform Cable USB II

DS593 (v1.2.1) March 17, 2011

8

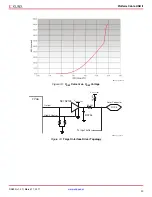

iMPACT 7.1i (and later) provides a feature wherein the BSDL file of each device in a target JTAG chain is scanned to

determine the maximum Boundary-Scan clock (JTAG TCK) frequency. iMPACT 7.1i (and later) automatically restricts the

available TCK_CCLK_SCK selections to frequencies less than or equal to the slowest device in the chain. By default,

iMPACT 7.1i (or later) selects either 6 MHz or the highest common frequency when any device in the JTAG chain is not

capable of 6 MHz operation.

shows the maximum supported JTAG TCK frequency for a variety of Xilinx devices. See

the device data sheet or BSDL file for maximum JTAG TCK specifications.

Note:

Certain Xilinx design tools and iMPACT versions earlier than 7.1i do not restrict the TCK_CCLK_SCK selections in JTAG mode.

Accordingly, users should take care to select a TCK_CCLK_SCK frequency matching the JTAG TCK specifications for the slowest device

in the target chain.

In Slave Serial or Direct SPI Configuration mode, the TCK_CCLK_SCK speed can be set to any one of the available

selections. By default, the TCK_CCLK_SCK speed is set to 6 MHz. Users should take care to select a TCK_CCLK_SCK

frequency matching the Slave Serial clock (CCLK or SPI clock) specification of the target device.

Table 3:

Maximum JTAG Clock Frequencies

Device Family

Maximum JTAG Clock

Frequency (MHz)

XC9500/XL/XV

10

XPLA3

10

CoolRunner-II

33

XC18V00

10

XCF00S/XCF00P

15

Virtex

33

Virtex-II

33

Virtex-II Pro

33

Virtex-4

33

Virtex-5

33

Spartan

5

Spartan-II

33

Spartan-3

33

Spartan-3A

33

Spartan-3AN

(50, 200 and 400 densities)

33

Spartan-3AN

(700 and 1400 densities)

20

Spartan-3E

30