PCI Express Control Plane TRD

www.xilinx.com

23

UG918 (v2017.2) July 18, 2017

Chapter 3:

Bringing Up the Design

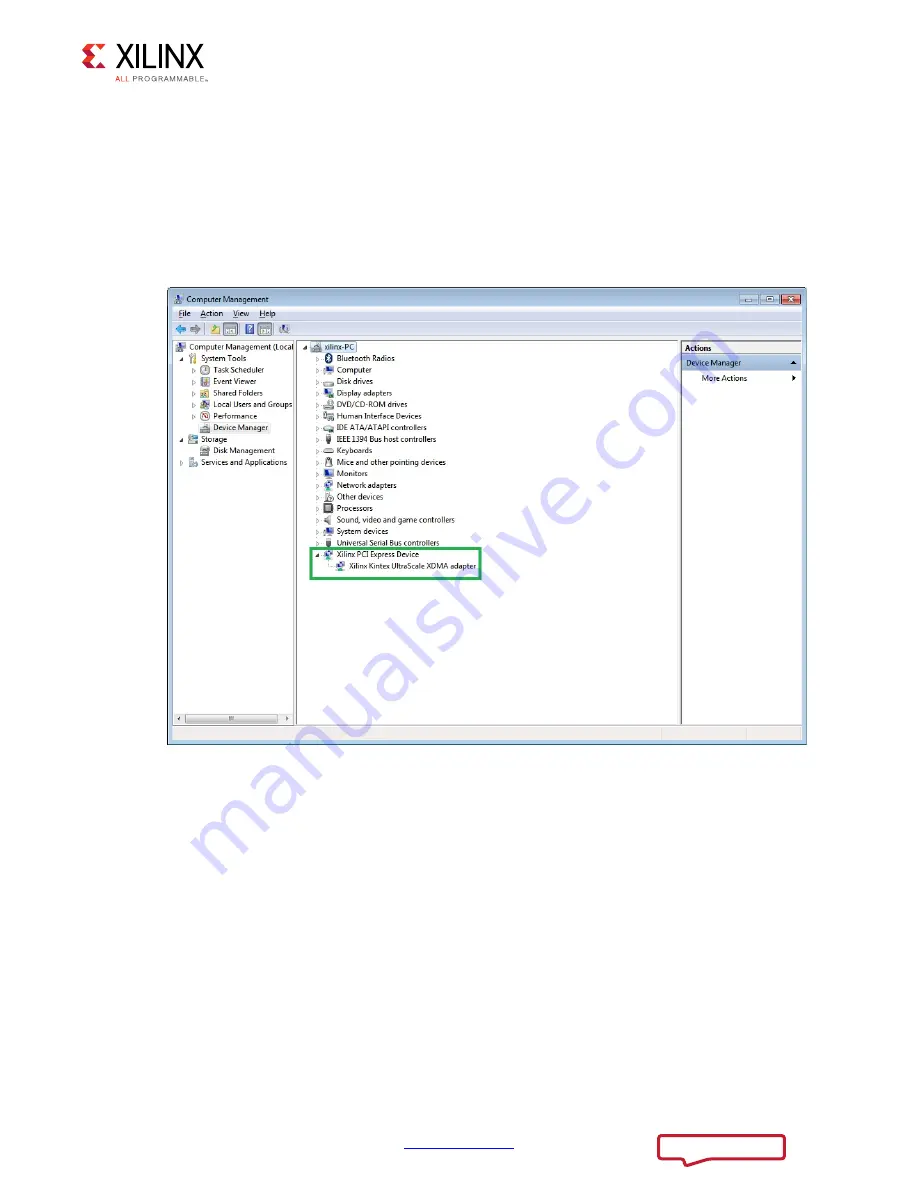

Run the Design on a Windows 7 Host Computer

After booting the Windows OS, follow these steps:

1. Repeat the steps in section

Disable Driver Signature Enforcement, page 9

.

2. Open Device Manager (click

Start > devmgmt.msc

then press

Enter

) and look for the

Xilinx PCI Express Device as shown in

Figure 3-9

.

X-Ref Target - Figure 3-9

Figure 3-9:

Xilinx PCI Express Device in Device Manager

UG918_c3_11_040715

Send Feedback